"내 칩(My Chip) 설계 교실" 설치 제안

본 제안은 오픈-소스 반도체 설계 자동화 도구를 활용하여 "내 칩을 내 책상 위에서(My-Chip on My-Desk)" 설계하고 검증하며 테스트까지 수행할 수 있는 역량을 갖추기 위한 교육안이다.

[주] 이 제안은 어떠한 기관에 국한되지 않고 누구에게나 열려 있습니다. 학습에 필요한 자료는 깃 허브 저장소[링크]에 공개되어 있으니 널리 활용되길 바랍니다. 이 제안을 수용할 의사가 있는 기관 또는 개인 중 도움이 필요할 경우 연락 주십시요. 질문 뿐만 아니라 조언, 오류 신고 등 언재나 환영 합니다.

동기

오픈-소스 컴퓨팅 도구들이 충분히 성숙되어 상용 툴을 대체하기에 이르자 프로그래밍 언어와 소프트웨어 개발은 전공자들의 전유물이 아니게 되었다. 오히려 비전공자들의 아이디어 구현이 빛을 내고 있기도하다. 반도체 설계도 예외가 아니다. 오픈-소스 반도체 설계 도구들도 발전을 거듭하여 시스템 수준 알고리즘에서 합성과 자동 배치배선 그리고 최종 레이아웃 생성까지 수행할 수 있는 체계를 갖췄다. 이에 비전공자들도 자신의 고유 칩을 만들수 있는 환경이 충분히 성숙되었다.

참고: [OpenROAD Project] /

[Toward an Open-Source Digital Flow: First Learnings from the OpenROAD Project]

FPGA 들이 저렴한 가격으로 널리 보급되어 반도체 설계 "덕후(enthusiast)", 또는 "메이커(Maker)"들이 등장하고 이제는 "반도체 설계"가 취미의 영역에 진입했다고 할 정도다. 예전에 유로였던 FPGA 개발 도구들도 무료로 사용 할 수 있도록 개방되는 추세다. FPGA 벤더에서 배포하는 개발도구 패키지 내에 오픈-소스 도구가 상당부분 차지하고 있음은 물론이다. 이에 덧붙여 국내에는 무료 MPW 사업 "내 칩 제작 서비스"가 수행되고 있고, 해외에서는 "닥치고 ASIC(Keep Calm & make ASIC)"이라는 기치아래 저렴하게 내 칩을 제작해주는 "Tiny Tapeout"서비스가 실시되고 있다. 이럼에도 국내 고등교육기관의 반도체 설계 교육 과정은 이러한 오픈-소스 개발 환경을 충분히 활용하지 못한다.

오픈-소스와 상용 도구의 개방(또는 저가공급)정책으로 반도체 설계 교육의 큰 장애가 되어왔던 고가의 설계 소프트웨어(EDA Tool) 라이센스 문제는 상당히 해소 되었다고 할 수 있다. 또다른 애로점으로 ASIC의 공정 기간을 들고 있다. 설계 데이터(레이아웃 DB)를 칩 제조 공장에 제출하고 실제 칩이 나오기까지 공정 기간이 4~6개월 가량 소요된다. 공정기간이 긴 탓에 교육과정을 꾸리는데 어려움이 있다고 한다. 이에 덧붙여 생활속에서 느끼는 발전된 반도체 기술과 교실에서 배우는 내용 사이의 엄청난 추상성 격차는 쉽게 극복하기 어렵다. 이런 상황에서 학부 학생들에게 교과서에 등장하는 각종 최신 공학적 방법론을 실습없이 이해하라는 것은 부당하다. 이러한 애로점(교육자재의 부족, 긴 공정기간, 학과목 간의 연계 부족)을 해소하고 반도체 설계 역량을 강화하기 위한 방안으로 "내 칩 설계 교실" 개설을 아래와 같이 제안한다.

내 칩 설계 교실

회로(아날로그 및 디지털)설계와 소프트웨어 프로그래밍(C++, Python) 및 하드웨어 기술(Verilog, VHDL)용 컴퓨팅 언어는 현재 대학의 교육과정에 모두 포함되어있다. 이들 과목이 칩 설계에 통합되지 못하여 마치 반도체 설계와는 무관한 듯이 여겨지는 실정이다. 이를 극복하기 위하여 "내 칩 설계 교실"을 운영하고자 한다. 이 "교실"에서는 약 6개월에 걸쳐 칩 설계를 Top-Down 방식으로 수행한다.

"내 칩 반도체 설계교실"의 설계 방법론(오른쪽 그림)과 VLSI 시스템 설계의 교과서에 등장하는 Y- 차트(왼쪽 그림)의 비교. 시스템 수준(System Level), 레지스터 트랜스퍼 수준(RTL, Register Transfer Level), 회로 및 레이아웃 수준(Circuit & Layout) 그리고 칩 테스트(Chip Test)까지 반도체 설계 전 과정을 실습을 통해 학습힌다.

학습 전략:

- "내 칩 MPW" 응모(접수) 2회: 학습 초기에 1차, 학습 후 2차

- 제시된 예제로 반도체 설계 방법론을 익히기

- 칩이 제작되어 나오기까지 수개월이 걸려 학습 공백을 피하기 위해,

- 오픈-소스 반도체 설계 도구를 익히면서 "내 칩 MPW"에 응모(1차 접수)

- 학습자 스스로 설계를 준비하기 어렵다면 준비된 예제를 사용

- 동일한 예제라도 설계 도구에 주어지는 옵션에 따라 상이한 레이아웃이 생성되므로,

- 예제 따라하기를 통해 반도체 설계 플로우와 설계 자동화 도구의 사용법 학습

- 칩이 제작되어 나올때까지 반도체 설계 전 과정 학습

- C/C++, Python 및 베릴로그 언어로 알고리즘 기술 및 합성과 시뮬레이션 기법을 학습

- SystemC/C++ 와 베릴로그 Co-Simulation 테스트 벤치 작성 기법 학습

- FPGA+Arduino 활용 Co-Emulation 검증 기법 학습

- 칩이 제작되어 출고되는 즉시 테스트를 실시할 수 있도록 준비

- HLS(High-Level Synthesis) 고급 설계 기법 학습

- C++로 기술된 알고리즘을 RTL로 합성

- Co-Simulation 테스트 벤치

- FPGA 구현 후 Co-Emulation (테스트벤치 재활용)

- ETRI050 노드로 GDS 생성

학습 목표:

"내 칩 설계교실" 학습을 마친 후,

- 반도체 산업 생태계에서 설계와 검증의 의미를 이해한다.- 반도체 설계 과정을 이해한다.

- VLSI System Y-Diagram을 설명할 수 있다(Gajski-Kuhn chart).

- "추상화 수준"의 의미를 이해한다.

(System Level vs. Register Transfer Level vs. Circuit-Level)

- "내 칩"을 설계하여 MPW에 응모(접수)한다(2차).

- 상용 반도체 설계 도구 교육(IDEC 등) 수강시 이해도를 높인다.

학습 일정:

단계1: 오픈-소스 도구 사용 반도체 설계 과정의 이해

- 반도체 설계가 이뤄지는 과정(Design Flow) 이해

- 오픈-소스 반도체 설계 도구 사용법 익히기

- 예제를 활용하여 GDS 생성 후 "내 칩 제작 서비스" 접수 (1차)

단계2: 반도체 설계용 컴퓨팅/개발환경 이해

- 리눅스 운영체제와 Command-Line Interface 익히기

- Tcl 스크립트 작성법

- Makefile 작성법

- C++, Python 심화 학습

단계3: 베릴로그 언어 알고리즘 기술 및 검증

- 베릴로그 언어 이해 및 심화학습

* 오픈-소스 베릴로그 시뮬레이터: iVerilog, Verilator(베릴로그 SystemC/C++변환기)

- C++ 언어와 SystemC 테스트 벤치 작성법

- 이종 시스템 설계 언어를 혼용한 Co-Simulation 방법(Verilog VPI+SystemC/C++)

- FPGA+아듀이노+라즈베리 파이 활용 이종 모델 사이의 Co-Emulation

(테스트벤치/소프트웨어+FPGA 연동/하드웨어)

단계4: 베릴로그 합성기와 자동 배치배선

- 오픈-소스 합성기(Yosys)의 이해 및 로그 해석

- 합성 후 네트리스트의 이해 및 시뮬레이션

- 자동 배치배선 도구(GrayWolf & QRouter)의 옵션 이해

- 외부공급 셀(GPIO & PCell) 들여오기

- 레이아웃 GDS 검토(Magic & Klayout)

단계5: 표준 셀 레이아웃

- 회로도 작성(XSchem)

- 오픈-소스 도구로 레이아웃 그리기(Magic 툴 사용법)

* Magic은 레이아웃에서 회로 네트리스트(트랜지스터 및 RC 성분)추출 가능

- 표준 셀 레이아웃 및 회로 시뮬레이션(ngSPICE)

- 표준 셀의 설계 자동화 도구 연계(Liberty, LEF 형식 이해) 방법

* 오픈-소스 베릴로그 합성기(Yosys), 자동 배치(GrayWolf) 배선기(QRouter)

단계6: 사인-오프의 이해

- LVS:Layout-Versus-Schematic 검사

- DRC:Design Rule Check 검사

- Stacked Via 검사

- "내 칩 서비스" 파운드리와 DRC 교차 검사(Caliber 툴 로그 해석)

단계7: 칩 테스트

- 테스트벤치 재사용 기법

- SystemC/베릴로그 테스트 벤치와 FPGA 연동 인터페이스

- 아듀이노 DUE 펌웨어 작성: 테스트 벡터 생성, 출력 획득 및 시현

* Arduino DUE FreeRTOS 활용(필요시)

- 디버깅용 측정장치 자작: 로직 아날라이져, 오실로 스코프

단계8: 고수준 합성(High-Level Synthesis)

- C/C++ 언어로 기술된 고 추상화 수준 알고리즘(설계)의 RTL 합성과 FPGA 검증

- FPGA 하드웨어용 병렬 프로그래밍을 위한 C++ 코드 최적화

- 고위합성(HLS)으로 얻은 RTL의 분석 및 최적화

- ETRI050 노드 적용 레이아웃 생성

단계9: "내 칩" 제작 응모 (2차)

- "내 칩 제작 서비스"의 MPW 표준 칩 요건에 맞추기

- 학습 단계별 실습 보고서

- "내 칩" MPW 제작 응모(1, 2차)및 테스트 결과 보고서

교육에 활용될 예제의 구성

교육에 사용될 각 예제는 아래와 같은 구성을 갖춘다.

1. 추상화 수준별 모델링 기법에 따라 알고리즘이 기술될 것

- Un-Timed C-Model

- Timed SystemC Model

- Verilog RTL Model

2. 각 모델의 테스트 벤치가 작성되어 있을 것

- C++/SystemC/Verilog 혼합 테스트 벤치 작성

3. RTL 모델이 기능검증될 것

- C++로 기술된 알고리즘에서 RTL로 수동 변환

- SystemC 테스트 벤치에 FPGA 에뮬레이션

4. FPGA 에뮬레이션을 수행할 것

- 칩 테스트 준비

5. ETRI050 테크-노드에 맞춰 레이아웃 생성 될 것

- 합성 스크립트

- 자동 배치배선 스크립트

- LVS 와 DRC, 적층 비아검사 스크립트

- 공정 제출용 Chip-Top GDS 생성

- 공정 DRC 검토 후 확인 받을 것(옵션)

- 합성 후 네트 시뮬레이션이 수행되어야 함

- 타이밍 시뮬레이션 수행(옵션)

6. C++ 모델 합성(옵션)

- Vitis-HLS 도구 사용 C++를 RTL 로 합성

- HLS로 합성된 RTL을 여러 FPGA에 구현(Xilinx/Altera/Gowin)

- HLS로 합성된 RTL을 ETRI050 디자인 킷으로 합성 및 자동 배치배선

- ETRI050으로 합성된 네트리스트와 SystemC 테스트벤치 Co-Simulation

7. 모든 과정(추상화 수준)을 수행하고 재현 가능한 스크립트가 준비될 것

- Makefile

예제의 예

학습을 위해 준비될 예제는 아래와 같다.

- FIR8 : 8-Tap FIR Filter

- ALU8: 8-비트 범용 ALU

- Pong-Game: 간단한 탁구 비디오 게임기

- CPU6502: 8 비트 마이크로 프로세서

- (흥미있는 예제 계속 추가/수료생 설계물 포함)

탁구 비디오 게임 예제의 Co-Simulation 및 Co-Emulation

https://youtu.be/3liwrc6pmU4?si=pRq8rO8HAETE5ZWz

CPU6502 예제의 Co-Simulation 및 Co-Emulation을 통해 Apple BASIC 작동

https://youtu.be/41fe34rDZ78?si=BQYJDhebucVlX97y

------------------------------------

FPGA 에뮬레이션 키트(교보재)

현재 각 대학에서 상용 레이아웃 툴을 교육용으로 라이센스 하고 있는데 5카피에 연간 1천만원 가량 이라고 한다. 상용 툴은 설치후 활용하려면 관리비가 드는데 이를 포함한 가격인지 알수 없다. 상용 레이아웃 툴을 도입한다 해도 교육과 관리(PDK 지원 등)가 없으면 칩 제작에는 무용지물이다. 위의 비용으로 온-사이트 교육을 지원 받기는 어려울 것이다. 교육 목적의 레이아웃 툴을 IDEC을 통해 공급 받는데 수량이 모자라 따로 학교마다 구입한다는데 사업비를 허비한다는 생각을 지울 수가 없다. 상용 툴이 취업을 대비하여 회사에서 사용하니 어쩔 수 없다는 말들을 하지만 대학내에 상용툴을 회사에서 요구하는 만큼 활용하고 교육할 수 있는 환경이 되어 있는지도 의문이다. 본 "교실"의 과정을 마치고 IDEC 에서 실시하는 각종 상용 도구의 무료교육에 참여하면 성과를 얻을 것이다.

상용 설계 도구의 라이센스 비용으로 학생들에게 교보재로 FPGA와 아듀이노 보드를 포함한 에뮬레이션 검증 키트를 제공하여 맘껏 쓰게 하는 편이 좋을 것이다. 에뮬레이션 키트는 이미 방안을 마련하여 놓았다.

학습자에게 1인당 1세트로 제공된 FPGA 에뮬레이션 키트는 실습비나 소모재 비용으로 충당하여 소실과 고장을 두려워 하지 않고 맘껏 활용 될 수 있도록 한다.

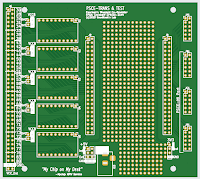

다양한 조합의 FPGA와 마이크로 컨트롤러 보드 활용 반도체 설계 검증 에뮬레이터 키트를 개발했다. FPGA와 MCU 보드는 기성품을 사용하고 통합(응용) 보드는 누구나 쉽게 조립(땜질) 할 수 있도록 2.54mm 피치 헤더핀을 사용하여 PCB 제작하였다.

- FPGA: Gowin GW-25K/Xilinx Artix7/Altera Cyclone

- MCU: Arduino DUE/ESP32/Raspberry Pi PICO

가장 저렴한 구성은 다음과 같다.

- Altera Cyclone EP4CE6C8(144-Pin TQFP) 모듈과 통합보드

Cyclone IV EP4CE6 는 로직 엘리먼트 6천개, 내장 메모리 270키로 비트로 용량이 다소 작다.

- JTAG 케이블

FPGA 다운로더. Xilinx 케이블 이지만 호환성이 뛰어나 범용 JTAG 케이블로 사용할 수 있다.

Digilent HS2로 작동, Xilinx 및 Altera FPGA 다운로더로 사용

- Arduino DUE 모듈과 어댑터 보드

ARM-M3 코어, 512K바이트 롬, 96K 바이트 램 내장

디지털 IO 54개(PWM 가능 12개), 아날로그 IO(ADC 6채널, DAC 2채널)

- 자작 오실로스코프/로직 아날라이져 Scoppy PI Pico와 입출력 보드

Scoppy는 안드로이드 앱이다. 휴대전화를 오실로스코프/로직아날라이져의 표시장치로 활용

"내 칩 제작 서비스"의 표준 패키지 28-핀 SOP 칩 테스트용 소켓과 프로브 용 클립

FPGA와 MCU 모듈 등 기성부품들의 통합 보드들은 중국의 샘플 업체를 통해 PCB 제작하였다. 3종의 보드 각 5매 샘플 제작에 UPS 배송료 포함 3.5만원 이다. 잡자재(핀 헤더, 전원 케이블 등)을 포함하면 재료비는 약 15만원/세트 가량 들 것으로 예상한다. 회로도와 PCB 자료 그리고 모델링 인터페이스 소프트웨어/아듀이노 펌웨어와 베릴로그 RTL, C++ HLS 예제들은 모두 깃-허브에 공개되어있다.

https://github.com/GoodKook/ETRI-0.5um-CMOS-MPW-Std-Cell-DK.git

-----------------------------------------

자료공개 원칙

디자인 킷과 예제(문서를 포함하여)는 깃-허브 저장소에 모두 공개함을 원칙으로 한다. 위 교실에 참여한 학습자의 작품은 완성도를 갖춰 크리에이티브 커먼즈/저작자표시-비영리-변경가능(Creative Commons/BY-NC)에 준하여 공개하는데 동의할 것.

https://creativecommons.org/licenses/by-nc/2.0/kr/