"MPW에 지원 하려는데 설계 도구 지원 되나요?"라는 질문을 하기전에,

반도체 산업이라 하면 떠오르는 정형이 있다. 온갖 장치들과 운송 장비들이 누비는 깔끔한 공장 내부와 그 사이에서 온몸을 하얀 방진복으로 두른 노동자들의 모습은 어쩐지 환상적이다. 자동화된 기계들이 착착 움직이는 모습, 거기에 더해 몽환적인 조명까지 마치 SF 영화의 미래세계를 보는 것 같다. 어디 반도체 산업 뿐이겠는가. 화면에 소스 코드 리스트를 띄워놓고 심각한 표정을 짓는 프로그래머, 칠판에 난해해 보이는 기호들을 나열해 놓고는 서로 풀어보라며 설전을 벌이는 과학자들의 모습을 보며 멋지다는 생각을 해봤을 것이다. 저 멋진 화면에 끼고 싶다는 생각에 '이공계'를 선택하고 이글을 쓰고 있다. 객쩍은 이야기로 시작하는 이유는 그 정형화된 모습은 산업 전반에 극히 일부분이라는 점을 말하고 싶기 때문이다. 해당 분야에 아무것도 모르는 방송 종사자, 영상 제작자들이 현란한 화면이랍시며 골라내 보여준 탓에 세뇌됐다.

반도체 강국이라는 우리나라는 정부 차원에서 '내칩 MPW' 사업을 진행 하고 있다. 무료로 학생들의 설계를 받아 반도체를 제작해 준다고 한다. 사업 공고문을 보면 '아날로그' 기반 CMOS 직접회로를 무료로 제작해 준단다. CMOS 공정에 굳이 '아날로그'만 된다는 법은 없지 않을까 싶어 문의해 봤다. 회로야 아날로그가 되었든 디지털이든 CMOS 회로를 그리고 레이아웃 GDS 제출하면 되겠느냐고 문의 했더니 그렇단다.

'내칩 MPW'는 회로도면을 그려오면 반도체로 제작해 주는 사업이다. 설계자가 알아서 그려오라는 말이다. 도면을 그리려면 도구(소프트웨어)와 기초자료가 있어야 한다. 공정의 물리적 특성을 보여주는 기초자료는 제공되지만 어떤 도구를 쓸지는 설계자의 선택이다. 설계를 위해 선택한 도구에서 요구하는 라이브러리를 준비하는 것도 큰 일꺼리다. 설계자는 자신이 선택한 도구에 맟춰 공정 기초자료를 기반으로 라이브러리를 제작해야 한다. 제조공장에서 다수의 설계도구마다 요구하는 양식의 라이브러리(또는 환경설정)를 제공하기는 곤란하지 않은가. 그것도 무료로 칩을 제작해 준다는데 툴마다 다를 디자인 킷(상당한 비용이 소요됨)까지 마련해 달라고 하는 것은 무리다.

디지털 회로로 MPW에 지원하기 위해 회로를 그리기로 하고 찾아보니 하드웨어 언어 합성기를 비롯하여 다양한 도구가 필요하다는데 가격이 만만치 않다. 다행히 '오픈-소스' 도구들이 있었다. 이들의 사용료 역시 무료지만 '내칩 MPW'의 공정에 맞는 라이브러리는 없다. 어쨌든 설계도구도 무료, 제조도 무료다. 나만의 반도체 칩을 가져보겠다는 꿈을 이루려는데 라이브러리가 없다고 포기할 수는 없기에 만들기로 했다.

알고리즘을 묘사한 기능은 높은 추상화 수준의 컴퓨팅 언어로 기술하고 이를 훨씬 낮은 수준의 회로도면으로 바꿔야 한다. 수천개의 트랜지스터로 구성될 회로도를 한번에 그려낼 자신이 없으므로 자동화 도구를 쓰기로 한다. 십여개 미만의 트랜지스터 회로는 손수 그려 표준 셀 라이브러리로 준비했다. 이를 합성기라는 도구에 연동 시키려니 여간한 일이 아니다. 트랜지스터 수준의 회로도를 컴퓨팅 언어 컴파일러(합성기라고 부르는)에 연동시키려면 '리버티(Liberty)'라는 표준 셀 라이브러리 정의 파일이 있어야 한단다. 이에 더하여 네트 시뮬레이션용 베릴로그(Verilog) 모델이 필요하다. 합성기도 소프트웨어 이므로 버그가 없다고 확신할 수 없으니 추상화 수준의 변경이 발생하면 반드시 검증절차를 거쳐야 하기 때문이다. 그뿐인가, 표준 셀 들의 자동 배치와 배선에 필요한 라이브러리 교환 LEF(Library Exchange Format) 파일(자동 배선 규칙과 표준 셀의 기하학적 정의, footprint), 도면 자동 생성용 후 DRC(Design Rule Check)와 LVS(Layout-vs.-Schematic) 검증을 위한 표준 셀의 회로도(SPICE netlist)들이 필요하다. 이들을 한데 모아 디자인 킷(Design-Kit)이라 한다.

디자인 킷 만들기에 필요한 지식은 대학의 전공수업에서 이미 다 배웠다. 전자회로, 논리회로 설계와 SPICE 시뮬레이션, 반도체 공정, VLSI 설계, 컴퓨팅 언어와 컴파일러, 하드웨어 언어와 합성기 등등. 공짜로 나만의 칩을 만들어 준다는데 이정도 수고는 해야하지 않겠나? 몇달간의 노력끝에 마침내 디자인 킷을 만들어 냈다. 이를 활용하여 레이아웃을 생성하여 공정에 제출하기에 이르럿다. 2023년 첫 내칩 MPW에 참여한 학생의 소감을 들어보자. 2024년 하계 전자공학회 학술대회에서 특별 세션으로 구두발표 예정이다.

"MPW 프로젝트 소감/지하은(경희대학교 전자공학과 3학년)"

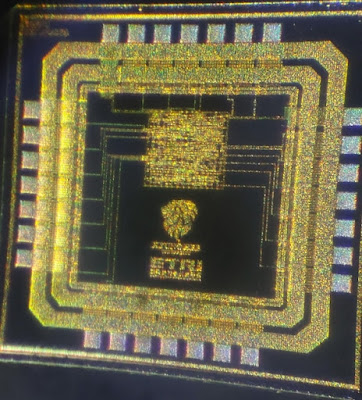

수개월 후 마침내 공정을 마친 칩을 제공받았다. 처음 해보는 칩이라 아주 간단한 설계여서 공간이 남아 그림을 넣었다. 칩에 고유의 표시를 넣는 경우가 종종 있다. Chip Art 혹은 Chip Graffiti라고 하는데 실리콘 위의 부활절 달걀인(Easter Egg) 셈이다. 누가봐도 세상에 하나뿐인 내 칩(My Chip)이다.

테스트를 해보니 정말 아쉽게도 칩은 동작하지 않았다. 공정을 해준 ETRI의 도움을 받아 레이아웃을 분석해 보니 디자인 킷에 실수가 있음을 발견했다. 설계물의 코어는 자체 제작한 디자인 킷을 썼으나 입출력 패드는 공정 측에서 PDK의 일부로 라이브러리를 제공 받았는데 GDS 형식이다. 오픈-소스 레이아웃 도구 Magic 에서 이를 들여와야 해서 변환용 테크 파일을 작성했는데 여기에 오류가 있었다.

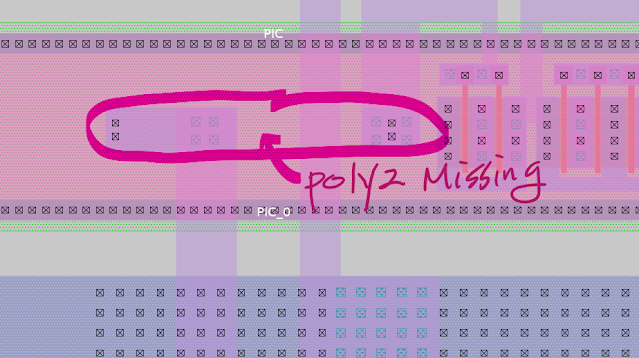

'내칩 MPW'의 공정은 2중 폴리실리콘에 3층 메탈이다. 대개 Poly2는 아날로그 회로를 꾸밀때 컨덴서와 저항의 용도로 사용한다고 배웠기에 그런줄 았았다. 그런데 디지털 입력 패드 셀 PIC 에 Poly2가 입력 전류 제한용 저항으로 사용되었다는 것을 미쳐 확인하지 못했기에 변환 룰에 Poly2 레이어를 빼먹었던 것이다. 나중에야 제공된 GDS를 KLayout(이역시 오픈소스다) 도구로 들여다보니 분명히 13번 레이어가 사용된 것을 확인했다.

실수한 테크 파일을 통해 PIC 를 읽었더니 Poly2 레이어가 빠진채다.

변환 룰을 수정하고 읽었더니 Poly2 저항이 제대로 보인다. 그런데 하필 레이어 이름이 pseudo_rpoly2 라니.

[주] 수정된 디자인 킷, https://github.com/GoodKook/ETRI-0.5um-CMOS-MPW-Std-Cell-DK.git

실리콘 검증까지 마친 디자인 킷을 만들겠다는 포부에 다소 '스크래치'가 가긴 했으나 첫술에 배부를 수는 없는 노릇이니 될때까지 시도해 보기로 한다.

반도체 업계에서 활동하는 현직 베테랑 중에 표준 셀을 그리고, 디자인 킷을 제작하고, RTL 설계에서 합성기, 레이아웃 마침내 테스트까지 '내칩'을 제작해본 경험을 가진 설계자는 많지 않다. 반도체 산업의 광범위한 생태계에서 한 부분에 종사할 따름이다. '내칩 MPW' 사업은 '풀 커스텀'으로 제출된 도면을 받아 공짜로 칩을 제작해 준다. 설계도구의 디자인 킷은 각자 알아서 마련해야 한다. 그러려면 반도체 설계 자동화 도구들의 속내를 들여다 보게된다. 여러 추상화 단계마다 제각각인 오픈 소스 도구들 사이에 호환성 검증, 파일 변환 등의 작업이 필요할텐데 일일이 수정할 수는 없는 노릇이다. 이를 간편히 수행할 각종 스크립트나 유틸리티를 작성하게 되는데 쉘 스크립트, python, Tcl 등 익히 알고있는 수단을 동원하자. 일례로, 적층된 비아(stacked via)는 흔히 허용되지만 '내칩 MPW'의 공정은 절대 금지되어 있다. 경희대학교 디자인 킷에는 자동 P&R로 생성된 레이아웃에서 이를 찾아내는 파이썬 유틸리티를 포함해 여러 스크립트를 가지고 있다. 디지털 칩은 다수의 입출력 핀들이 사용된다. '내칩 MPW'에서 제작해주는 칩은 20여개의 핀에 불과 하다지만 막상 이를 테스트 하려면 막막하다. 오픈 소스 마이크로 컨트롤러 보드 '아듀이노 메가'는 40여개의 디지털 핀을 사용할 수 있다. 이를 이용하면 다신호 프로그래머블 시그널 생성기 및 로직 아날라이져를 저렴하게 꾸밀 수 있다. 설계의 검증을 위해 사용한 테스트 벤치를 칩 테스트 용도로 사용할 수 있다. 요즘 하드웨어 시뮬레이터는 C++/SystemC로 작성한 함수를 호출 할 수 있는 API들이 필수다. 컴퓨터의 주변 장치에 접근하는 방법은 대부분의 운영체제에서 허용하기 때문에 C++ 함수에서 구동 소프트웨어를 호출하면 아듀이노 보드를 통해 '내칩'과 신호를 주고 받을 수 있다. 테스트벤치 재활용을 칩 테스트까지 확장해 볼 수 있다. 규모는 비록 작지만 반도체 설계의 전과정을 수행해 볼 수 있다. 이는 반도체 산업의 전분야를 체험해 봤다고 주장해도 무리는 아니다.

[주] 오픈 소스 도구들의 디자인 킷 활용한 시뮬레이션, Arduino-FPGA 에뮬레이션, 레이아웃 생성, 패드 프레임 등 일련의 실습을 수행 할 수 있도록 예제가 준비되어 있다. https://github.com/GoodKook/ETRI-0.5u-CMOS-MPW-DK-Example--ALU8.git

'내칩 MPW'는 공짜로 칩을 만들어 준다하고 설계도구는 오픈-소스를 공짜로 쓸 수 있다. 이 얼마나 설레지 않을 수 있으랴. 디자인 킷 정도는 만들어 쓰자. 그대신 책임은 스스로 진다. 여기서 책임이란 곧 돈이다. '내칩 MPW'는 이 비용이 무서워 감히 못해볼 짓을 공짜로 해볼 수 있는 천재일우의 기회를 제공한다. 전자공학을 배우며 이제껏 주워들은 것들을 총동원하여 엮을 기회다. 구슬이 서말이라도 꿰어야 보배라고 하지 않던가!