2023년 7월 주간 강좌 및 주간 세미나 결과 보고

2023년 7월 중 3회의 세미나와 4회의 강좌를 주관 실시하였다. 이에 다음과 같이 보고함.

주관/작성자: 국일호 (goodkook@khu.ac.kr)

________________

목차

- 주간 세미나

- 주간 강좌

- 총평

- 8월 계획

- 제안

________________

I. 주간 세미나

- 반도체 설계자로서 알아야 할 기본소양 중 하나로 컴퓨팅 언어로 기술하는 반도체 회로와 시뮬레이션을 소개 한다.

- 아래와 같이 3회 실시하였다.

[1] 반도체 설계자가 알아야 할 컴퓨팅 언어

- 컴퓨팅 언어의 종류와 분류

- 소프트웨어 개발 언어

- 하드웨어 기술 언어

- 상세내용: https://fun-teaching-goodkook.blogspot.com/2023/07/2023-07-19.html

[2] 반도체 설계자, C++ 얼마나 알아야 하나?

- 반도체 설계자에게 C++는 필수 요건이다.

- C++ 의 특징 살펴보기

- 상세내용: https://fun-teaching-goodkook.blogspot.com/2023/07/c-2023-07-12.html

[3] 소프트웨어 언어와 하드웨어 언어

- 용도가 다른 두 컴퓨팅 언어의 차이점을 비교하고 특징을 살펴본다.

- Verilog 언어의 특징 살펴보기

- 상세내용: https://fun-teaching-goodkook.blogspot.com/2023/07/2023-07-05.html

II. 주간 강좌

- 기초 전자회로의 시뮬레이션에 SPICE를 활용한다.

- 전자회로 시뮬레이터 SPICE의 시뮬레이션 명령 사용법을 배운다.

- SPICE 기초강좌 3회, Verilog HDL 과 SystemC의 Co-Simulation 소개 1회

[1] SPICE 기초 [1/3]

- SPICE의 Transient simulation 기법

- 저항 브릿지, 분압회로

- Behavioral Voltage source 표현법

- https://fun-teaching-goodkook.blogspot.com/2023/07/spice-13-2023-07-05.html

[2] SPICE 기초 [2/3]

- SPICE의 AC Analysis (Fourier Analysis) 기법

- LC 공진 회로

- Behavioral description의 시뮬레이션 테스트 기법: AM 변조 및 선형 검파

- 사용자 정의 변수 사용: Frequency sweep 기법

- SPICE의 네트리스트(netlist) 기술과 시뮬레이션 명령(dot-commands, directives)

- https://fun-teaching-goodkook.blogspot.com/2023/07/spice-2023-07-12.html

[3] SPICE 기초 [3/3]

- 트랜지스터의 I-V 특성곡선 읽기

- C 급 전파 증폭기 회로

- SPICE의 시뮬레이션 명령으로 증폭회로의 특성 (효율) 분석

- https://fun-teaching-goodkook.blogspot.com/2023/07/spice-33-2023-07-19.html

[4] 병행 시뮬레이션(Co-Simulation)

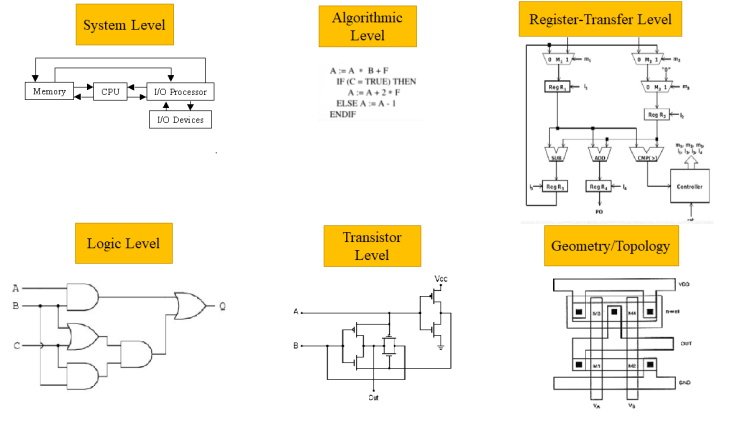

- Abstraction Level의 이해 (System specification 에서 Chip 까지)

- Design domain의 이해 (Behavioral-Structural-Physical)

- Domain 사이의 전환: Synthesis & Analysis vs. Generation & Extraction

- Abstraction Level 전환: Refinement

- 시스템 수준 반도체 설계 검증 환경

- Verilog HDL 과 SystemC/C++로 구성하는 Co-Simulation 소개

- https://fun-teaching-goodkook.blogspot.com/2023/07/co-simulation-2023-07-26.html

III. 총평

세미나와 강좌 시간 중 질문을 유도하였으나 많은 질문을 이끌어 내지는 못했다. 학습자들의 적극적인 참여를 위해 흥미로운 예제를 개발 할 필요가 있다. 그중 몇개의 질문은 아래와 같았다.

- 교외 학습 기관에서 실시하는 유료 온라인 강좌가 도움이 될까?

- 반도체 설계 도구들의 사용법을 알고 싶다.

교외 온라인 강의가 유료로 진행된다고 한다. 기업체 인사 담당자의 세미나에서 반도체 설계를 두루 섭렵해야 한다는 이야기를 듣고 교내 강좌로 부족하다는 느낌을 가졌기 때문 이리라. 학부 과정의 정규 수업만으로 전자회로, 설계언어, 레이아웃과 테스트까지 전과정을 익히기는 불가능 하다. 학생들 개인의 노력에 따라 성취의 정도가 다를 것은 당연하다. 하지만 현실을 알면서 저리 이야기 해서 학생들을 불안케 할 것 까지 있을까 라는 의문이 든다.

반도체 설계도구의 사용법(설계언어 포함)을 배웠더라도 막상 뭔가 해보려면 막막할 것이다. 그 도구를 가지고 뭔가 해 볼 동기 부여가 필요하다. 연습을 통해 능력치가 향상된다는 점은 반도체 설계라 해서 예외가 아닐 테니까.

학생들의 관심과 도전심을 불러 일으키기 위해 흥미로운 예제와 과제를 개발 할 필요가 있다. 이에 8월 중에 다음과 같은 예제를 개발 하여 강좌에 활용 토록 하겠다.

IV. 8월 계획

8월중 실시될 강좌의 주안점은 “Co-Simulation” 이다. 이미 정규 수업을 통해 Verilog HDL과 C++ 언어는 알고 있을 것이다. 7월중 세미나를 통해 반도체 설계자로서 요구되는 안목을 소개했다. 예제 중심으로 강좌를 실시 한다.

[1] Project 6502

- 개인 컴퓨터의 시작이 되었던 APPLE ][에 사용된 CPU가 6502 다. 지금도 에뮬레이션 소프트웨어를 통해 수 많은 추억의 게임을 즐기는 인구가 상당하다. 6502 의 Verilog RTL 과 SystemC/C++ 의 검증 환경을 구성한다.

[2] Project Z80

- Zilog Z80 역시 수많은 게임기에 적용되었던 CPU다. Verilog RTL과 SystemC/C++ 검증 환경을 구성한다.

[3] Project RISC-V

- RISC-V는 모든 컴퓨터 구조 교과서에 등장하는 개방형 RISC 머신이다. Verilog RTL과 SystemC/C++ 검증 환경을 구성한다.

8월중 실시될 세미나는 설계도구를 소개한다.

[1] Magic, VLSI Layout Tool

- 풀-커스텀 MPW에 참여 권장.

[2] QuestaSim, HDL/SystemC Simulator

- 두말할 필요가 없는 세계 1위의 시뮬레이터

[3] VisualStudio 2022, C++ compiler & debugger

- 반도체 설계의 검증 환경 구축 기법

V. 제안

향후 1년간(2023-2024) 실시할 주간 세미나 및 강좌 계획

취지

반도체 설계 도구의 사용법 배우기를 지양하고 더 높은 단계로 도약하기 위해 다음과 같이 '주간 세미나'와 '주간 강좌'를 계획 하고 있다.

- [주간 세미나]는 1회성 세미나다. 설계도구를 소개하고 기법을 익히는 시간이 되도록 한다.

- [주간 강좌]는 3~6회의 연속 강좌 입니다. 설계도구의 기초 사용법과 디지털 신호처리 중 멀티미디어, 통신시스템과 관련된 알고리즘의 기초를 강의 합니다.

세미나와 강좌의 원칙

- 정규 교과목에서 취하는 '전 과정을 기초부터 모든것'을 다루겠다는 방식을 피하고 실용성을 추구한다. 이론은 이미 정규 수업에서 들어 봤을 것이므로 요약하며,

- 의미있는 예제 중심으로 직접 수행해 보도록 한다. 그 과정에서 수강자 스스로 새로운 아이디어를 구상해 낼 수 있길 바란다.

- 이론 수업과 더블어 회로제작과 측정장비의 활용은 물론 필요하다면 시험장치 제작까지 이어질 수 있을 것이다.

- 세미나와 강좌의 내용은 온-라인 상에 모두 공개하여 스스로 학습에 도움이 되도록 할 것이며 오프-라인 세미나 시간에 질문과 토론이 이뤄지길 바란다.

- 학점과정이 아닌 만큼 자유롭고 적극적인 참여를 기대 한다.

- '주간강좌'와 '주간세미나'는 모두에게 열려 있다. 누구든 막론하고 참여 환영한다.

다룰 내용

설계도구의 사용법은 간단히하며 다양한 활용을 다룬다. 최근 반도체 설계 도구의 발전을 보건데 사용법은 단순해졌고 알고리즘의 구현을 강조하고 있습니다. 사용법이 아닌 설계자의 의도를 명확히 해주는 것이 중요 하다. 적용될 하드웨어에 맞춰 알고리즘의 계산특성을 파악하고 수정해 줘야 최상의 결과(입출력 조건, 하드웨어 크기, 수행 클럭 수, 소모전력)를 얻을 수 있다. 통신 시스템, 인공지능, 기계학습등에 적용되는 알고리즘을 다루도록 합니다.

- C++ / SystemC, Python, HDL(Hardware Description Language)

- SoC Design Flow / 추상화 수준 / TLM(Transaction Level Modeling)

- 검증환경 작성 기법 (Co-Simulation / Emulation)

- HDL-RTL 합성 및 HLS (High-Level Synthesis): FPGA & ASIC

- Radio System 및 SDR (Software Defined Radio) : Digital Signal Processing

- 인공지능 / 기계학습 알고리즘: (AI & ML Algorithms)

FPGA는 물리학, 우주과학, 항공기계, 의료공학 분야에도 많이 활용되고 있다. 제 분야에 학생 연구자들에게도 반도체 설계 교육을 제공 할 수 있을 것이며 반도체 설계 전공 학생들에게는 다양한 취업 방향을 모색하는 동기가 될 것이다. 이와 관련하여 교내외 연구자들의 참여를 기대 합니다.

설계도구 목록

학습자의 개인 컴퓨터를 적극 활용하여 '자기주도' 학습을 돕고자 '무료' 설계 도구를 활용 한다. 아래에 소개할 '무료' 도구들은 단순한 교육용 도구들이 아니다. 상용의 도구들 이지만 제작사들의 관대함 덕에 '무료'로 교육용으로 사용할 수 있도록 배포되고 있습니다. 그외 GNU 정신에 의거 '집단지성'의 힘으로 완성된 수준 높은 도구들 이다.

1. C, C++

- MicrosoftVisual Studio Community Edition

- Linux GCC G++

2. Python

- Jupyter Notebook

3. Wolfram(Mathematica)

4. HDL (Hardware Description Language)

- QuestaSim

5. SDR (Software Defined Radio)

- GNU Radio / Linux

6. Layout Tool

- Magic / Linux

7. SPICE

- LT-Spice

8. RTL-HDL & HLS(High Level Synthesis)

- Xilinx Vitis HLS

- Microchips Libero/Smart HLS

9. Microprocessor

- Arduino IDE (AVR)

- STM-32 GNU toolchain(ARM)

- uC/OS (Real-Time OS)