"Verilog-Verilator-SystemC 방법론 기초"

[6] "내 칩 MPW" 요건에 맞춘 FIR 필터의 PE 설계

"Verilog-Verilator-SystemC 방법론 기초"는 "내 칩(My Chip) MPW 서비스": 오픈-소스 도구 활용 반도체 설계 특별과정 중 두번째 강좌로서 베릴로그(Verilog)와 오픈-소스 시뮬레이션 도구 Verilator 그리고 시스템 수준 검증 방법론 SystemC의 입문 과정이다. 컴퓨팅 언어를 활용한 디지털 회로의 설계와 검증을 다룬다(Quantative approach to digital circuit design using computing language and Open-Source EDA tools).

강의 내용은 아래와 같다.

[1] 도구 설치 [링크]

[2] 설계 언어 Verilog 와 검증 언어 SystemC/C++[링크]

[3] 하드웨어 기술 언어의 코딩 스타일[링크]

[4] 실습: 쉬프트 레지스터 [링크]

[5] 실습: FIR 필터 [링크]

[6] "내 칩 MPW" 요건에 맞춘 FIR 필터의 PE 설계[링크]

[부록] FIR 필터 PE의 "내 칩MPW" 제출용 GDS 생성[링크]

----------------------------------------------------------

목차

I. 개요

II. 처리요소 PE의 입출력 패드 제한(Pad Limit)

III. 입출력이 분할된 PE의 RTL 설계와 전송 규약

IV. 테스트벤치

V. 실습. FIR 필터의 PE 설계

a. 테스트벤치 빌드(Build Testbench)

b. 시뮬레이터 실행(Run FIR filter simulator)

c. 베릴로그 PE 모델의 내부 신호 추적(Trace internal signal of Verilated model)

-----------------------------------------------------------

I. 개요

"내 칩 MPW" 서비스의 공고문에 따르면 제작해주는 칩의 면적과 입출력 패드의 제한은 아래와 같다.

- 칩 크기: 1.9mm x 1.9mm

* 설계 면적 ~1.5mm x 1.5mm, GPIO 사용시 설계 면적 ~1.0mmx1.0mm

- 패키지 칩을 제공 받을 경우 표준칩 배치 (PDK 내 “MPW_PAD_28pin”) 사용

앞서 설계한 8-탭 FIR 필터는 "내 칩 MPW" 서비스를 통해 제작하기에 너무 크다. FIR 필터는 확장 가능한 파이프라인 병렬처리 구조다. 별도의 외부 제어장치 없이 처리요소(PE, Processing-Element)만을 직렬로 연결하여 쉽게 확장 할 수 있는 시스톨릭 어레이(Systolic Array) 구조다. 처리요소를 칩으로 제작 하기로 한다.

"내 칩 MPW" 서비스는 공정을 마친 칩을 28핀 SOP 패키지로 제공한다.

약 20여개의 패키지가 제공되는 만큼 다수의 PE들을 조합하여 배열 구조를 구성할 수 있다. 비록 "내 칩 MPW" 서비스의 단일 칩 규모(크기)는 작지만 여러 프로젝트를 조합하면 상당 규모의 알고리즘 구현도 가능할 것이다.

II. 처리요소 PE의 입출력 패드 제한(Pad Limit)

앞서 설계한 FIR 필터 어레이의 PE에 대하여 입출력 포트의 수를 살펴보자. 입력으로 32핀, 출력 24핀 그리고 클럭이 있다. 여기에 전원(VDD)과 접지(GND)까지 합치면 총 79개 패드가 필요하다. 내 칩 MPW 의 28핀 패드 제한을 훌쩍 넘어선다.

처리요소 PE에 필요한 입출력 포트의 수를 유지한 채 각 포트의 비트 폭을 나눠 패드 제한(pad limit)을 해결하기로 한다. 입력과 출력을 4비트씩 분할하여 전체 27개의 패드를 사용한다.

8비트 입출력 Xin과 Xout 을 각각 4비트씩 분할하면 전송에 2 클럭이 들지만 16비트 Yin과 Yout 은 4클럭을 차지한다. 입출력을 분할한 탓에 파이프라인 인터벌(interval)이 1에서 4로 증가할 것으로 예상된다. 4비트씩 분할한 입출력 포트와 타이밍은 아래와 같다.

III. 입출력이 분할된 PE의 RTL 설계와 전송 규약

인접 PE 사이에 전송되는 데이터 중 MAC에 해당하는 Yin과 Yout 을 4 비트로 나눴다. 인터벌이 5로 증가한 PE의 RTL 베릴로그는 아래와 같다. 4비트 단위로 전송받은 Xin과 Yin을 쉬프트 레지스터로 받아 곱셈과 덧셈을 수행한 후 결과를 4비트씩 출력한다. PE 내에서 별도의 FSM 제어장치(FSM controller) 없이 파이프라인 처리가 이어진다. PE 내부에 명령어 처리는 물론 FSM 제어기를 가지고 있지 않다. 단순한 1 비트 쉬프터가 입출력과 계산 절차를 맞춰주는 시퀀서(squencer) 역활을 한다. 입출력 포트를 4비트로 분할한 처리요소의 베릴로그 RTL은 아래와 같다.

처리요소 PE의 인터벌이 늘어났다. 입출력이 단지 클럭에 동기된 파이프라인이 아니다. 한 데이터를 여러 클럭에 걸쳐 분할 전송하는 방식으로 바뀌었다. 안전한 분할전송을 위해 첫 4비트 전송이 시작되는 표시가 필요해졌다. 입출력 인터페이스(In/Out Interface)로 단방향 핸드쉐이크 방식을 채택했다. 전송 규약(protocol)은 아래와 같다.

전송할 데이터의 시작을 이웃 PE에 알리는 Rdy에 이어 연속적으로 Xin과 Yin가 이어진다. Xin은 8비트 이므로 4개의 전송 클럭 중 첫 2 클럭 동안에서 유효하다. PE들은 파이프라인 배열이므로 Rdy 와 Vld 그리고 Xin과 Xout, Yin 과 Yout의 프로토콜 타이밍은 동일하다.

제작할 칩의 조건(면적과 패드 갯수)에 따라 PE의 내부 구조가 변경되었다. 그 외에도 응용에 따라 변경되는 입출력 방법(인접 모듈과 인터페이스, 프로토콜)은 RTL 설계에 직접적 영향을 준다. 입출력 인터페이스는 알고리즘의 사양(문서 사양과 C++)에서 쉽게 간과되어 선 않된다.

IV. 테스트벤치

처리요소들 사이의 데이터 전송규칙(protocol)이 변경 되었지만 배열 구조는 동일하다. 칩으로 제작할 부분은 PE다. PE를 제외한 FIR 필터의 배열 구조는 SystemC로 기술하기로 한다.

모듈 크래스 sc_fir8은 행위 묘사를 위한 소속함수와 감응이 없는 순전히 구조적 모듈이다. 구성자 내에 Verilator로 변환한 베릴로그 PE의 SystemC 모듈들을 배열로 사례화하고 연결하였다.

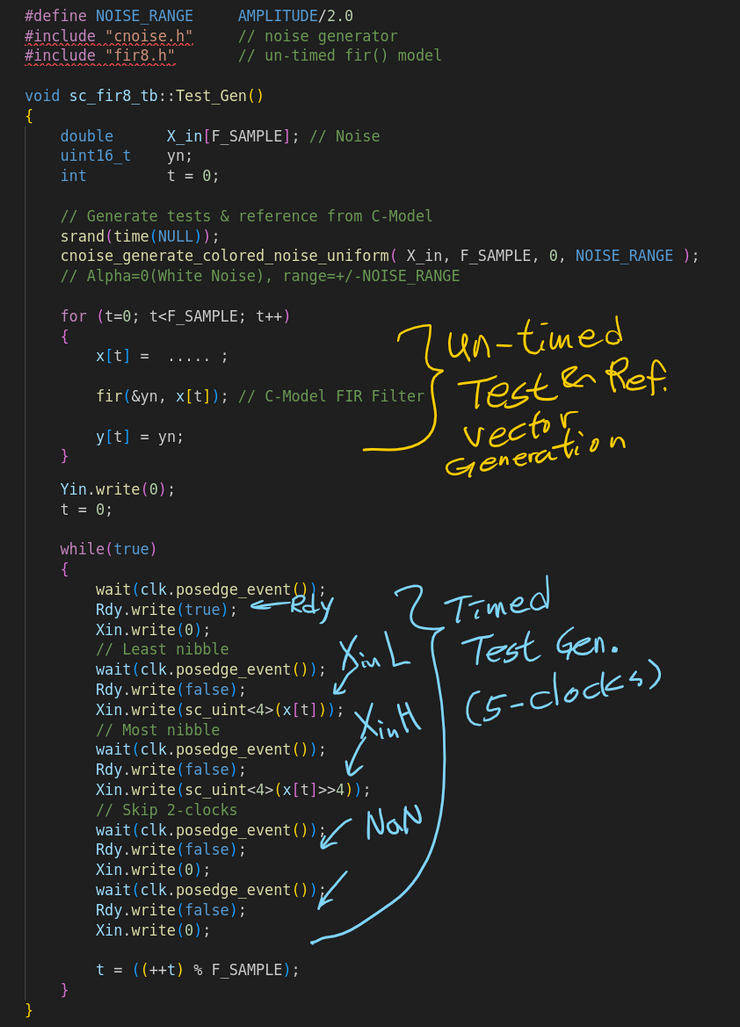

테스트벤치에서 클럭 동기 테스트 신호 생성 쓰레드 함수 Test_Gen()은 다음과 같다. 알고리즘 시험을 위해 작성해둔 언-타임드 fir()로 표준 참고 데이터를 생성하는 것은 앞의 경우(인터벌이 1인 파이프라인 배열 구조)와 동일하다. 인터벌이 늘었고 인터페이스 타이밍이 변경되었다. 테스트용 신호를 새롭게 설계한 PE의 전송 프로토콜에 맞춰 생성한다.

검증용 쓰레드 함수 Test_ Mon()은 다음과 같다. FIR 배열의 마지막 PE 출력을 클럭 동기화 프로토콜에 맞춰 읽어 표준 값과 비교한다.

V. 실습. FIR 필터의 PE 설계

"내 칩 MPW" 에 최적화된 FIR 필터를 시뮬레이션을 수행한다. 예제 코드는 아래 링크를 통해 받을 수 있다.

https://github.com/GoodKook/ETRI-0.5um-CMOS-MPW-Std-Cell-DK/tree/main/Tutorials/2-6_Lab4_FIR_PE

또는 경희대학교 디자인 킷[1]의 튜토리얼로 포함되어 있다.

[1] 경희대학교 디자인 킷/ETRI 0.5um Std-Cell DK, https://github.com/GoodKook/ETRI-0.5um-CMOS-MPW-Std-Cell-DK

a. 테스트벤치 빌드(Build Testbench)

RTL 베릴로그 PE를 SystemC로 변환한 후 테스트벤치를 컴파일하여 시뮬레이터를 빌드한다. 예제에 Makefile을 준비해 두었다.

예제의 시뮬레이션 디렉토리로 이동,

$ cd ~/ETRI050_DesignKit/Tutorials/2-6_Lab4_FIR_PE/simulation

메이크 수행,

$ make build

verilator --sc -Wall --trace --top-module fir_pe --exe --build \

-CFLAGS -std=c++17 -CFLAGS -g -CFLAGS -I../../../2-5_Lab3_FIR8/c_untimed \

-CFLAGS -DVCD_TRACE_FIR8 -CFLAGS -DVCD_TRACE_FIR8_TB \

-LDFLAGS -lm -LDFLAGS -lgsl \

../source/fir_pe.v ./sc_main.cpp \

./sc_fir8_tb.cpp ../../2-5_Lab3_FIR8/c_untimed/fir8.cpp \

../../2-5_Lab3_FIR8/c_untimed/cnoise.cpp

b. 시뮬레이터 실행

테스트 입력 Xin 과 계수곱과 누산 값 Yin 이 이웃한 PE 사이에 인터벌 5로 전송되는 것을 확인할 수 있다. 특히 Yin은 이전 PE의 누산되어야 하므로 Xin의 전송에 비하여 1 클럭 지연되고 있다.

c. 베릴로그 PE 모델의 내부 신호 추적

RTL 설계 중 디버깅을 하려면 베릴로그의 내부 신호를 들여다 봐야 하지만 변환된 모델을 SystemC에서 제공하는 방법으로 VCD 기록은 불가능 하다. 당연히 Verilator는 SystemC 모델로 변환된 베릴로그 PE의 내부 신호를 VCD 덤프 할 수 있는 방법을 제공한다.

어레이 구조 FIR 필터를 클럭의 시간순으로 살펴보면 아래와 같다.

Verilator의 VCD 기록을 보면서 PE 내부의 동작을 살펴보자. 아래 VCD는 FIR 배열에서 마지막 PE의 내부 동작을 보여준다. Xin은 인터벌 마다 이웃 PE에 전송되고 계수 Cin과 곱해진다. Yin 는 누산되어야 하므로 한 클럭 뒤이어 전송되고 있다.

댓글 없음:

댓글 쓰기