"VLSI 레이아웃 설계 기초"

[3]: Magic, CMOS 인버터 레이아웃 작성과 회로 추출

[알림] 아래 내용중 질문, 지적, 보강 등 어떤 사항도 환영 합니다.

"VLSI 레이아웃 설계 기초"는 "내 칩(My Chip) MPW 서비스": 오픈-소스 도구 활용 반도체 설계 특별과정 중 첫번째 강좌다. 오픈 소스 도구의 기초적인 사용법과 레이아웃 설계와 검증을 정성적으로 다룬다(Quantative approach to VLSI layout design using Open-Source EDA tools).

강의 내용은 아래와 같다.

[1] 리눅스 및 VLSI 레이아웃 도구 설치 [링크]

[2] XSchem, CMOS 인버터 회로도 작성과 시뮬레이션 [링크]

[3] Magic, CMOS 인버터 레이아웃 작성과 회로추출 [링크]

[4] Netgen, 추출한 회로 비교(LVS) [링크]

[5] XSchem 실습: 인버터 회로도 (Schematic Design) [링크]

[6] Magic 실습: 인버터 레이아웃 (Layout Design) [링크]

[7] Netgen 실습: 네트리스트 비교 및 회로 시뮬레이션 [링크]

[8] Std-Cell 제작 실습: DFF-SR [링크]

------------------------------------------------------

목차

I. 학습개요

II. 반도체 제조 공정과 레이아웃의 이해

II-1. NSPL 0.5um 공정 단면도

II-2. n-MOSFET

II-3. p-MOSFET

II-4. 커페시터와 저항

II-5. 컨택(contact)과 비아(via)

II-6. 표준공정의 레이어 이름(Layers for Standard Process)

III. Magic의 사용법

III-1. 테크 파일

III-2. 환경 설정 파일

III-3. Magic 실행

III-4. 그리기 툴(모드)과 마우스 버튼의 용도

III-5. 기본 단축키

IV. 인버터 레이아웃 그리기

IV-1. 대화형 그리기 검사(interactive DRC)

IV-2. 레이어 이름 약칭(layer name)

IV-3. 자동생성 레이어

IV-4. 컨택과 비아 자동 생성

IV-5. 레이블 붙이기

V. 회로 네트리스트 추출

VI. 시뮬레이션

VII. 결론

I. 학습개요

VLSI 레이아웃 그리기 오픈-소스 도구는 Magic이다. 등장한 이래 지난 40여년간 꾸준히 발전해 왔고 지금도 여전히 갱신되고 있다[1]. Magic으로 인버터 회로의 반도체 제조 도면(레이아웃)을 그리기로 한다. 단순히 도면 그리기에 더하여 SPICE 시뮬레이션 가능한 트랜지스터 회로의 네트리스트를 추출한다. 실제 제조용 도면이므로 배선간 존재할 기생(parasite) 인턱턴스(L)과 케페시턴스(C)도 함께 추출된다. 추출한 네트리스트로 SPICE 회로 시뮬레이션을 해본다.

II. 반도체 제조 공정과 레이아웃의 이해

레이아웃을 그리기 전에 반도체가 제조되는 과정을 이해해 보자. 반도체 공정을 설명하는 여러 동영상, 심지어 쉽게 설명한다며 만화로 보여주기도 한다. 그중 가장 알차게 축약하여 설명한 동영상이 있어 소개한다. 약 13분 분량이다.

Chip Manufacturing - How are Microchips made? | Infineon, https://youtu.be/bor0qLifjz4?si=_E04jMdSl9d5Mfo5

레이아웃은 트랜지스터 회로를 제조용 평면도다. 이 평면도에 따라 반도체 물질과 금속을 적층하여 트랜지스터를 만든다. 평면도와 적층도의 관계 그리고 트랜지스터의 원리를 아주 잘설명한 동영상도 소개한다. 약 7분짜리 동영상이다.

CMOS Tech: NMOS and PMOS Transistors in CMOS Inverter (3-D View), https://youtu.be/oSrUsM0hoPs?si=TwaiKRg-jpOCOMVk

위의 두 동영상으로 한학기 분량의 반도체 공정 수업을 요약해 놓았다고 해도 과언이 아니다. 어디가서 반도체 설계한다고 말할 때 자신감을 갖기 바란다.

II-1. NSPL 0.5um 공정 단면도

NSPL 0.5um CMOS 설계규칙(Design Rule) 문서에서 설명하는 공정 단면도는 아래와 같다. 실리콘 실리콘 바닥(subtrate)에 n 형 도전성 물질 및 p 형 도전성 물질을 형성한다. n형 도전체(n-conductive)는 실리콘보다 전자가 하나 적은 보론(boron)을 p형 도전체(p-conductive)는 실리콘보다 전자가 하나 많은 인(phosporus)을 실리콘에 주입한 물질이다. 이온화된(플라즈마) 보론 혹은 인을 고온으로 가열한 실리콘 원판에 뿌리주면 침투해 들어간다. 공정에서는 침투시킨다는 의미로 p(또는 n) 임플란트(implant)라고 하고 레이아웃으로 그릴때 해당 평면 영역을 p(또는 n) 디퓨젼(diffusion)이라고 한다. 같은 것을 관점에 따라 달리 칭하는 경우가 흔히 있다.

폴리 실리콘은 mos 트랜지스터의 채널(전자가 이동하는 경로)에 해당하는 영역을 한정하여 전극을 붙이는 용도다. 굳이 물질 특성을 말하자면 중성화 실리콘이라고 해야겠다. 폴리 실리콘은 금속보다 다소 높은 저항을 갖는다. 채널은 트랜지스터의 게이트에 해당한다. 드레인과 소스에는 직접 금속을 붙이지만 게이트에 해당하는 폴리 실리콘은 산화물 부도체(oxide)로 간격을 띄워준다. MOS(Metalic-Oxide-Silicon)라는 이름이 이 적층 구조에서 기인하였다.

II-2. n-MOSFET

n-형 mos 트랜지스터의 적층 구조는 아래와 같다. p-형 바닥(subtrate)에 n 형 도전체를 간격을 두고 심어(implant) 양측을 각각 소스와 드레인으로 삼는다. 양의 바이어스 전압이 게이트에 걸면 p 채널이 도통된다. 채널 양쪽의 n 디퓨젼(NSD 레이어)은 완전히 대칭이므로 회로도 상으로 D와 S는 의미가 없다. 드레인과 소스를 구분하자면 전류원을 두는 전극에 따라 결정된다고 하겠다. 게이트에 바이어스가 걸리지 않을 경우 채널이 플로팅 되는 꼴이 되어 스위칭 성능을 저하시킨다. 이를 방지하기 위해 n-형 mos의 채널이 될 p형 바닥(subtrate)을 VSS 에 연결하였다. p-탭(tab)으로 표시되어 있다. 용도를 의미하는 것으로 제조공정상 p-우물(P-WELL)에 p-형 디퓨전을 심어 놓은 것이다.

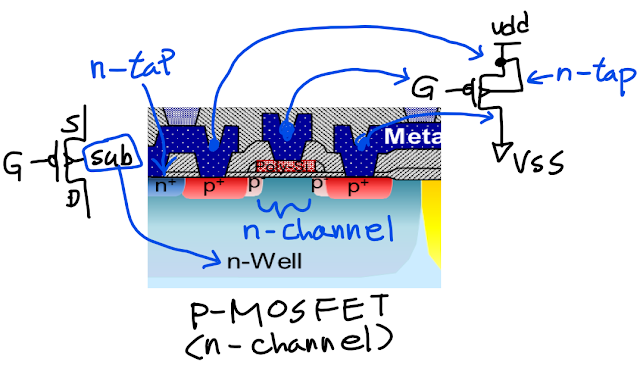

II-3. p-MOSFET

p 형 MOS 트랜지스터의 적층 구조는 아래와 같다. 전자들이 흘러갈 통로(channel)를 형성하기 위해 n-형 우물(N-WELL)을 깊게 팠다. 소스와 드레인은 p-디퓨전(pdiff)으로 형성되며 채널이 플로팅 되지 않도록 n-탭을 통해 VDD에 연결되었다.

트랜지스터의 바닥(subtrate)을 반드시 VDD나 VSS에 두어야 하는것은 아니다. 채널이 게이트의 바이어스 전압에 의해 스위치 역활을 효과적으로 하길 바라는 디지털 회로에서 적용된다.

II-4. 커페시터와 저항

커페시터(콘덴서)는 마주보는 두 극판 사이에 전하를 하전 시키는 구조다. 극판 사이가 가까울 수록 하전용량이 커진다. 아주 얇게 깔린 산화물 부도체(oxide) 사이에 폴리 실리콘 1과 2층을 마주보게 놓아 커페시터를 만든다. 용량은 마주보는 두 폴리 실리콘의 면적에 따라 결정된다. 저항은 얇은 폴리 실리콘의 길이로 정해진다. 커페시터와 저항의 구조는 아래 그림과 같다. 용량은 단면도보다 평면도의 모습으로 결정된다.

"내 칩 MPW"의 공정에 아날로그 CMOS 라고 명시된 이유로 폴리 실리콘을 2개 층이 포함되었기 때문이다. 저항과 케페시터를 위한 2중 폴리 실리콘층을 가지고 있다.

II-5. 컨택(contact)과 비아(via)

반도체 적층 구조상 가장 아랫 부분의 실리콘에 각종 회로 요소(트랜지스터 등)들이 놓인다. 금속으로 평면에 배치한 회로 부품들을 상호 연결한다. 이는 인쇄회로 기판과 완전히 동일한 의미다. NSPL 공정의 2P3M은 폴리 실리콘 층이 2개, 메탈이 3개층을 가졌다는 의미다. PCB로 보면 3중 기판인 셈이다. 실리콘(디퓨전 및 폴리)과 첫번째 금속 층과의 접점을 컨택(contact), 금속층 사이의 접점을 비아(via) 라고 한다.

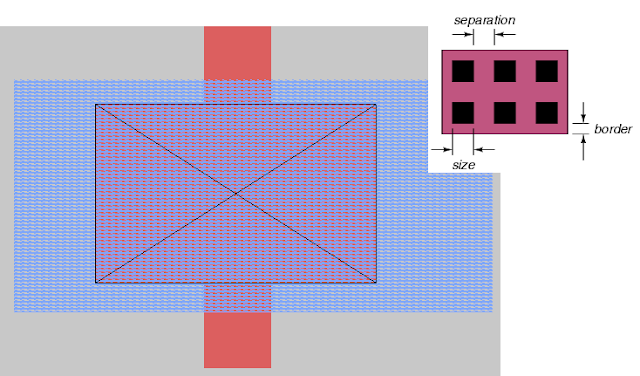

컨택과 비아의 단면 구조는 아래 그림과 같다. 서로다른 두 배선층 사이을 연결하기 위한 구멍을 컷(cut), 구멍을 둘러싼 금속을 익스텐션(extension) 또는 행(hang)이라고 한다. 평면도에서 컷과 익스텐션을 합쳐 비아 또는 컨택이라고 한다.

레이아웃 그리기 규칙(Design Rule) 문서에 컷과 익스텐션의 간격과 넓이를 각각 규정하고 있으나 Magic의 레이아웃은 컷과 익스텐션을 합쳐 비아 또는 컨택으로 표시한다. 최종 GDS 도면을 생성 할때 비아로 표기된 중앙에 컷을 자동으로 뚫는다. 컷을 뚫는 규칙도 테크 파일에 규정되어 있다.

배선 금속층의 맨 아랫층과 중간 층 그리고 최상층을 모두 연결하는 경우 겹친 비아(Stacked VIA)라고 한다. 배선 공간의 절약에 매우 유리하다. 하지만 정밀 공정이 요구된다. "내 칩 MPW"의 NSPL 0.5um 공정은 겹친 비아를 금지한다.

II-6. 표준공정의 레이어 이름(Layers for Standard Process)

전자회로의 레이아웃을 그리는 설계자는 디자인 룰을 읽을 수 있어야 한다. 그리기 규칙은 대부분 기하학적인 규정으로 길이(length)와 너비(width) 그리고 최소 간격(separation)들이다. 막상 규정집을 펼쳐보면 생소한 레이어 이름들을 마주하게 된다. NSPL 0.5um CMOS 표준공정의 그리기 규정집에 등장하는 레이어 이름들을 보자.

KEY

다층의 레이어들을 쌓을 때 맞추기 위한 기준 점을 표시한다. 설계와 상관 없다.

NWELL

순수 실리콘 웨이퍼에 깊이 심어놓는 n 형 도전체 영역이다. p 형 트랜지스터의 채널 역활을 한다.

PWELL

순수 실리콘 웨이퍼에 깊이 심어놓는 p 형 도전체 영역이다. n 형 트랜지스터의 채널 역활을 한다.

CMOS 공정은 p 형 트랜지스터와 n 형 트랜지스터가 쌍으로 존재한다. 우물(WELL)은 트랜지스터의 채널이 될 바닥(subtrate 또는 body) 영역이다. 두 우물 중 하나를 그려주면 나머지는 자동 생성된다. CMOS 설계시 p-형 우물을 따로 그리지 않고 있는데 이는 자동 생성하기 때문이다. NSPL 설계 규칙 문서에 따르면 p-형 우물(PWELL)의 생성규칙은 아래와 같다.

PWELL = Or( AndNot (CHIPBOUNDRY, NWELL), PWELL)

기묘한 논리식 처럼 보이지만 결국 n-우물(NWELL)이 아닌곳은 모두 p-우물(PWELL)이라는 뜻이다. 위와 같은 방식의 표기법은 레이아웃 도구의 테크 파일에서도 볼 수 있다.

POLY1

첫번째 폴리 실리콘 층. 트랜지스터의 채널에 바이어스를 가하는 영역이다. 트랜지스터의 게이트에 해당한다.

POLY2

두번째 폴리 실리콘 층. 회로에 커페시터 또는 저항을 넣을 때 사용된다. POLY1 과 마주하는 영역이 케페시터가 된다. 디지털 회로에 거의 사용되지 않는다.

NSD

n형 디퓨전이다. n 형 트랜지스터의 드레인 또는 소스 측에 해당한다. p형 우물 위에 심어지는(implant) n 형 도전체 영역이다.

PSD

p형 디퓨전이다. p 형 트랜지스터의 드레인 또는 소스 측에 해당한다. n형 우물 위에 심어지는 p형 도전체 영역이다.

ESD

정전기 방지(Electrostatic Discharge)를 위한 조치를 위해 n형 우물을 깊이 박는 영역이다. 주로 입출력 패드 셀에서 볼 수 있다[8].

[출처] https://www.intechopen.com/chapters/66524

CONT

웨이퍼 상에 심어진 디퓨전 및 폴리 실리콘과 금속1과의 접점(contact)이다. 독립된 공정 층을 의미하는 것은 아니다. 실제 구멍에 해당하는 컷(cut)과 감싸는 금속(extensioon)을 포함한다.

METAL1

첫번째 금속층이다. 웨이퍼 상의 디퓨전과 폴리 실리콘의 배선에 쓰인다.

VIA1

금속 1과 금속 2층의 접점이다. 컷(cut)과 감싸는 금속(extensioon)을 포함한다.

METAL2

두번째 금속층이다. 전역 배선에 쓰인다. 전역 배선 중 수평(또는 수직) 배선을 담당한다.

VIA2

금속 2와 금속 3층의 접점이다. 컷(cut)과 감싸는 금속(extensioon)을 포함한다. 상층으로 올라갈수록 표면이 고르기 않기 때문에 컷의 크기가 커진다.

METAL3

세번째 금속층이다. 전역 배선에 쓰인다. 전역 배선 중 수직(또는 수평) 배선을 담당한다.

ACTIVE

트랜지스터가 놓이는 활성(ACTIVE) 영역이다. 공정에 필요한 독립된 층이지만 레이아웃을 그릴때 ACTIVE를 그려넣지 않는다. 레이아웃 도구에서 트랜지스터 채널과 디퓨젼을 합쳐 자동 생성된다. 이 층이 필요한 이유는 두껍게 쌓인 산화물층 트랜지스터 공정에 방해되지 않도록 깍아내기 위한 영역이다. n (또는 p) 우물에 디퓨젼을 심어 놓는 구멍을 뚫게 되는데(etching) 두껍게 쌓인 산화물 층이 이온화된 p+, n+ 가스가 내려 앉는데 방해되지 않도록 조금 더 깍는다. 아울러 트랜지스터의 게이트 전극이 될 폴리 실리콘이 채널 영역에 가깝게 내려 앉도록 해준다.

앞서 소개한 반도체 공정 동영상에서 7분10초에 잘 설명되고 있다. [https://youtu.be/bor0qLifjz4?si=4iJhl7drZHvmTgOo&t=431]

표준 공정의 레이어들을 살펴봤다. 설계자가 직접 그려야 하는 레이어도 있고 자동으로 생성되는 레이어도 있다. 경우에 따라서 별도의 레이어는 아니지만 용도에 따라 붙여진 가상 레이어도 있다. 예를들어 트랜지스터의 경우 폴리 실리콘이 덮고 있는 게이트에 해당하는 영역의 아랫부분은 n(또는 p)의 바닥(subtrate)이다. 양쪽으로 디퓨전이 자리하고 있어서 트랜지스터의 전자이동 채널의 역활을 한다. 레이아웃을 그리는 설계자에게 이를 알려주기 위해 nfet(ntransistor) 또는 pfet(ptransistor)로 표시하지만 실제 공정에 사용되는 레이어는 아니다. 이런 레이어를 가상 레이어(virtual layer)라고 한다.

컨택의 경우 접촉할 실리콘에 따라 레이어 이름을 달리 붙이는데 레이아웃을 그리는 설계자의 편의를 위한 구분이다. 결국 모두 같은 컨택 규칙이 적용된다. Magic에서 부르는 컨택의 이름은 아래와 같다.

pc - poly contact, p2c - poly2 contact

ndc - n-diffudion contact, nsc - n-subtrate contact

pdc - p-diffusion contact, psc - n-subtrate contact

레이아웃을 그리는 규칙을 디자인 룰이라 한다. 디자인 룰은 제조공장의 정밀도를 나타낸다. 선폭이 좁을 수록 같은 면적에 더 많은 회로를 넣을 수 있지만 공장의 정밀도가 따라주어야 한다. NSPL 0.5um 공정은 최소 선폭이 0.5 마이크로 미터라는 의미다. 레이아웃을 그리기 전에 디자인 룰을 기술한 문서를 읽어보길 권한다.

III. Magic의 사용법

VLSI 레이아웃은 반도체 공정에 사용되는 각 층을 평면에 그려놓은 것이다. 전자회로 기판 PCB(Printed Circuit Board)와 매우 유사하다. 다만 선폭이 매우 좁다. NSPL 0.5um 공정의 최소 선폭은 500nm 다.

III-1. 테크 파일

평면도는 그림판이나 심지어 모눈 종이에 그릴 수도 있다. 고해상도 사진을 찍어 축소하여 감광용 필름(photo-mask film)으로 사용한다.

축소의 정도는 반도체 제조시설의 정밀도에 달렸다. 반도체 제조공장은 정밀도를 감안 하여 그리기 규칙(Drsign Rule)을 제공하므로 이를 준수하여 평면도를 그려야 한다. NSPL 0.5um 공정의 평면도 그리기 규칙은 PDK에 포함되어 있다[2]. 이 규칙은 문서 형태로 제공된다. 레이아웃 도구에 설계 규칙을 적용 하려면 도구마다 제정된 방식으로 표현해 주어야 한다. 이 규칙 파일을 테크 파일(Tech-file)이라고 한다[3].

경희대학교 반도체 전공 트랙 디자인 킷[4]에 그리기 규칙 문서를 토대로 Magic 용 테크 파일을 작성해 두었다. 테크파일 명은 SCN3ME_SUBM.30.ETRI.tech 으로 ~/ETRI050_DesignKit/tech 에 있다.

III-2. 환경 설정 파일

Magic을 실행하면 현재 작업 폴더에서 환경 설정(RC, resource config.)파일을 찾는다. 주된 내용은 테크 파일의 위치와 라이브러리들이 위치한 경로를 지정한다. 그외 사용자 인터페이스로 단축키 등을 정의해 놓는다. Magic의 설정 파일명은 .magicrc 이다. 디자인 킷에 간단한 환경 설정 파일을 제공하므로 이를 가져다 쓰도록 한다. 아울러 이번 학습의 작업 디렉토리는 1-2_Inverter_Magic 이다.

$ cd

$ mkdir Tutorials

$ cd Tutorials; mkdir 1-2_Inverter_Magic

$ cd 1-2_Inverter_Magic

$ cp ~/ETRI050_DesignKit/tech/etri050.magicrc .magicrc

리눅스 파일 시스템에서 . 으로 시작하는 파일은 감춤파일(hidden file)이다. Magic 설정 파일 .magicrc 의 내용은 아래와 같다.

#-----------------------------------------------------

# .magicrc startup file for ETRI050 project

#-----------------------------------------------------

path sys +/usr/local/share/qflow/tech/etri050

tech load SCN3ME_SUBM.30.ETRI -noprompt

scalegrid 1 2

set GND gnd

set VDD vdd

drc euclidean on

drc off

addpath ~/ETRI050_DesignKit/digital_ETRI

addpath ~/ETRI050_DesignKit/pads_ETRI050

macro Control_XK_Pointer_Button4 {zoom 0.5}

macro Control_XK_Pointer_Button5 {zoom 2}

III-3. Magic 실행

Magic을 실행하면 두개의 창이 뜬다. 레이아웃 창과 명령창이다. 명령창은 Tcl/Tk 의 명령줄로 구현되었다.

$ magic -d XR

Magic을 실행 할 때 디스플레이 터미널 속성을 지정 할 수 있다. 명령줄 옵션 -d XR 은 그래픽 창이 X-윈도우 터미널 속성을 따르도록 한다. 속도는 느리지만 레이어 마다 컬러가 유려해 그림 편집시 피곤하지 않다. 디스플레이 옵션을 주지 않는 경우 해칭(그믈선)방식으로 레이어를 표현한다.

III-4. 그리기 툴(모드)과 마우스 버튼의 용도

Magic의 그리기 창은 4가지 모드(툴)로 작동한다. 모드 전환은 자판의 '스페이스(space)' 키다.

- 상자 모드(BOX Tool): 십자 모양의 마우스 포인터 커서. 박스를 쳐서 영역을 칠하는 등 레이어를 편집 하는 도구다.

- 배선 모드(WIRING Tool): 마우스 포인터 커서가 화살표로 표시된다. 그려진 레이어의 박스를 선택하여 끌고 다닐 수 있다.

- 네트리스트 모드(NETLIST Tool): X 모양의 마우스 포인터. 개체를 선택한다.

- 선택 모드(PICK Tool): 그려진 개체를 선택한다.

그림 그리기 응용 프로그램이 그렇듯 마우스가 가장 큰 역활을 한다. 다만 일반적인 마우스의 사용자 인터페이스 기능과 사뭇 다르다. 4가지 모드 중 주로 쓰이는 상자 도구와 배선 도구에서 마우스의 기능은 다음과 같다.

- 상자도구: 마우스 왼쪽 버튼은 상자의 좌측 하단 위치를 지정한다. 오른쪽 버튼은 상자의 오른쪽 위 좌표다. 마우스 중앙 버튼은 상자 내를 칠할 레이어를 고른다.

- 배선도구: 마우스 왼쪽 버튼은 끌고다닐 레이어를 선택한다. 오른쪽 버튼은 선택 취소. 중앙 버튼은 끌고다닌 상자 내부를 칠한다.

Magic의 레이어 그리기는 오직 직각 사각형(rectangular) 상자 만을 취급한다. 상자를 이어붙여 면을 표현하는 방식으로 '조각보 꿰메기(corner-stitch)' 라고 부른다. 상자를 저장할 때 벡터 형식을 취하지만 그래픽은 그림판 처럼 운용된다. 꼭지점 이동은 허용되지 않으며 고무줄(rubber-band) 늘이기나 줄이기도 허용되지 않는다. 현대 벡터 그래픽에 익숙한 사용자에게 다소 구식으로 불편할 수 있다.

III-5. 기본 단축키

레이아웃 그리기 창의 메뉴는 수많은 기능들에 비해 매우 단순하다. 기능들을 메뉴에 넣기보다 단축키로 처리하고 있다. 명령에 인수가 필요한 경우 명령 창에 긴 형식의 명령으로 입력한다. 단축키와 명령들을 모두 알기도 어렵고 그럴 필요도 없다. 다만 어떤 명령이 있는지 참고 [5]의 링크를 따라가 명령 일람표를 훓어보기 바란다.

마우스 사용법에 덧붙여 몇가지 단축키를 알아두면 유용하다. 당장 뭐라도 그려 보려면 당장 필요한 단축키 명령들이다.

's' - 선택(select). 마우스 포인터 아래에 놓은 개체를 선택. 두번 연달아 누를 경우 동일 배선을 모두 선택.

'b' - 상자의 정보(위치와 크기)를 명령창에 알려준다(box)

'd' - 선택한 상자 지우기(delete)

'u' - 앞서 실행한 명령 취소(undo)

'm' - 선택해 놓은 상자 이동(move)

'c' - 선택해 놓은 상자 복사(copy)

'v' - 전체 보기(view all) 현재 그려놓은 레이아웃을 한화면에 보여준다.

숫자 키패드의 기능들도 상당히 유용하다.

방향키 - 그림판 상하좌우로 이동. '쉬프트'와 함께 누르면 크게 이동.

숫자판 화살표 - 선택된 박스 상하좌우('8', '2', '4', '6') 이동.

숫자판 '5' - 현재 상자 내용으로 확대(Zoom box)

자판의 컨트롤 키를 누르고 마우스 휠을 돌려 화면 확대와 축소할 수 있도록 환경 설정 .magicrc 에 매크로로 정의해 놓았다.

macro Control_XK_Pointer_Button4 {zoom 0.5}

macro Control_XK_Pointer_Button5 {zoom 2}

Magic의 사용자 인터페이스로 오래된 Tcl/Tk를 사용하고 있지만 나름 장점도 있다. 사용자의 구미에 맞도록 설정과 스크립트 운용이 매우 자유롭다. 전통적으로 많은 상용 EDA 도구들이 Tcl 스크립트를 사용해왔다. Magic 의 영향이라고 한다.

IV. 인버터 레이아웃 그리기

공정에 대한 최소한의 상식을 가지고 레이아웃을 그려보자. 공정 규칙에 따라 일일이 자로 재가며 그릴수는 없는 노릇이다. 반도체 레이아웃 도구는 미리 작성한 그리기 규칙을 적용한다. 설계도구에서 사용할 그리기 규칙을 테크 파일이라 한다. Magic의 경우 테크 파일을 참조하여 대화형으로 규칙을 검사해준다.

IV-1. 대화형 그리기 검사(interactive DRC)

임의의 상자를 만든 후 p 디퓨전으로 칠했다. 그리고 대화형 DRC를 활성화 시켰더니 아래와 같은 모습이 나타났다. DRC 오류가 흰 점으로 표시되었다.

상자의 크기를 box 명령으로 알아보니 폭 0.3u, 높이 0.3um다. DRC 오류의 원인은 알아보자.

명령 drc 는 상자내의 그리기 규칙 검사다. 여러 옵션을 가지고 있다. 그중 why 로 이유를 물어보니 디퓨젼의 크기가 너무 작다고 알려준다. 명령들이 직관적이다.

IV-2. 레이어 이름 약칭(layer name)

그리기 규칙에 맞춰 p-MOSFET 를 그려보자. 상자를 위치한 후 paint 명령으로 레이어 이름을 주면 칠한다. 레이어 이름은 테크 파일에 정의되어 있다.

레이어 이름은 약칭으로 쓰이기도 하는데 예를 들어 pdiff는 p-diffusion, p는 poly silicon, m1은 Metal 1 등으로 상당히 직관적 이다. 그리기 창 좌측에 사용 가능한 레이어 이름과 표시 색이 나열되어 있으므로 레이어의 약칭을 몰라도 원하는 레이어를 찾아 선택할 수 있다.

IV-3. 자동생성 레이어

실제 공정에 필요한 레이어는 십여가지(NSPL의 표준공정은 14가지)이지만 Magic에 나열되어 있는 레이어의 종류는 상당히 많다. 설계자의 편의를 위해 만들어진 레이어들이 다수 포함되어 있다. 예를 들어 p-디퓨전 영역 위에 폴리 실리콘을 그리면 겹치는 공간은 자동적으로 p-MOSFET 이 되는데 이를 별도로 transistor 레이어로 정의해 놓고 있다.

레이어들이 겹칠 경우 자동 생성되는 규칙 역시 테크 파일의 compose 에 정의되어 있다. 다음은 변환 규칙의 일부다.

compose

compose nfet poly ndiff

compose pfet poly pdiff

compose nfet poly nsubstratendiff

compose pfet poly psubstratepdiff

......

paint ndiff nwell pdiff

......

paint psc nwell nsc

paint pfet pwell nfet

paint pdiff pwell ndiff

paint nsd pwell psd

paint nsc pwell psc

......

end

compose 규칙의 예를들면 ndiff에 poly 가 겹치면 nfet이 된다. 칠하기 규칙의 예로 ndiff 에 nwell 을 칠하면 pdiff 가 칠해진다. 하지만 nsc(nsubtratecontact)처럼 nwell에 ndiff를 칠하는 경우도 있다. 따라서 psc 에 nwell을 칠하면 nsc 가된다.

NWELL 위에 ndiff를 심을 이유는 없지만 n-tap을 다는 경우에 이를 허용하기 위해 nsc(nsubtratencontact) 레이어를 두고있다. psc의 경우도 마찬가지다.

IV-4. 컨택과 비아 자동 생성

확실한 접점(접점은 저항이 높다)을 위해 금속선에 다중 접점(multiple contact, via)을 사용한다(예를 들어 전원 계통). 접점을 일일이 붙이지 않고 자동으로 생성한다. Magic의 GDS 생성 규칙(cifout)에 접점의 컷을 만들어내는 규칙을 담고있다.

square border,size,separation

금속1과 폴리 실리콘의 컷 생성규칙의 예는 아래와 같다.

layer CCP pc/m1

squares 60 60 60

calma 31 0

Magic의 그리기에서는 pc(Poly contact)가 큰 X 표 상자로 그려지지만 GDS는 다중의 컷으로 생성된다.

IV-5. 레이블 붙이기

앞서 살펴 봤듯이 Magic은 디퓨젼과 폴리 실리콘이 겹쳐 놓으면 트랜지스터로 인지한다. 이 규칙에 따라 그려 놓은 그림으로부터 트랜지스터 회로도를 SPICE 네트리스트로 추출할 수 있다. 이 네트리스트는 LVS와 시뮬레이션에 이용된다.

네트리스트를 시뮬레이션, 자동배선 등 설계 자동화 도구에서 사용하려면 회로의 연결선에 고유 이름을 붙여 두어야 한다.

레이블 붙이는 명령은 label이다.

label vdd c m1

port make

위의 예는 선택한 메탈1(m1)의 상자 중앙(c)에 vdd로 레이블을 붙였다. 레이블을 붙이는 위치는 상하좌우 그리고 중앙을 옵션으로 지정할 수 있다. 시뮬레이션을 위해 하위 회로(sub-sirccuit)의 포트(port)까지 설정해 놓도록 하자.

V. 회로 네트리스트 추출

그림으로부터 회로를 추출해보자. 인버터의 각 연결선에 모두 레이블을 붙였다.

네트리스트 추출 명령은 extract 다. 내부 형식으로 추출 한 후 이를 SPICE 형식으로 변환 한다.

extract all

ext2spice format ngspice

ext2spice

추출된 SPICE 네트리스에 기생 LC 가 포함된다. 추출된 SPICE 네트리스트는 아래와 같다. 간단한 회로인데다 배선 경로도 매우 짧아서 입출력 부하 외에 추출된 기생(parasite) LC는 없다. 기생 LC 값은 공정의 특성으로 제공되는 PDK에 의거하여 Magic의 테크 파일의 extract 항목에 정의한다.

* NGSPICE file created from inverter.ext - technology: scmos

.option scale=0.15u

.subckt inverter in out vdd gnd

M1000 out in vdd vdd pfet w=12 l=4

+ ad=0.192n pd=56u as=0.18n ps=54u

M1001 out in gnd gnd nfet w=12 l=4

+ ad=0.168n pd=52u as=0.168n ps=52u

C0 out gnd 3.0088f

C1 in gnd 2.36385f

C2 vdd gnd 5.93253f

.ends

두 트랜지스터의 채널에 n 과 p 탭을 붙이지 않은 경우 추출된 네트리스트는 아래와 같다. 매우 작은 값이긴 하지만 기생 LC가 증가하는 모습을 볼 수 있다.

* NGSPICE file created from inverter.ext - technology: scmos

.option scale=0.15u

.subckt inverter in out vdd gnd

M1000 out in vdd w_n41_60# pfet w=12 l=4

+ ad=0.192n pd=56u as=0.18n ps=54u

M1001 out in gnd w_n1073741817_n1073741817# nfet w=12 l=4

+ ad=0.168n pd=52u as=0.168n ps=52u

C0 gnd w_n1073741817_n1073741817# 3.19299f

C1 out w_n1073741817_n1073741817# 3.0088f

C2 vdd w_n1073741817_n1073741817# 2.1312f

C3 in w_n1073741817_n1073741817# 2.36385f

C4 w_n41_60# w_n1073741817_n1073741817# 3.80133f

.ends

VI. 시뮬레이션

레이아웃에서 추출한 회로도를 하위 회로(sub-circuit)으로 두고 이를 테스트하는 환경(테스트벤치)을 아래와 같이 작성 하였다.

* NGSPICE TB

.include ~/ETRI050_DesignKit/tech/05cmos_model_240201.lib

.include inverter.spice

xinverter_0 in out VDD GND inverter

R0 VDD out 1Mega

VDD VDD GND 5

VIN in GND 0

.dc VIN 0 5.0 0.01

.save all

.control

run

plot in out

plot i(vdd)

.endc

.GLOBAL VDD

.GLOBAL GND

.end

NSPL 0.5um CMOS 공정의 SPICE 모델과 이어서 추출한 네트리스트를 들여왔다(.include 명령). 인버터를 사례화(instantiate) 한 후 입력 VIN에 0에서 5볼트까지 전압을 증가(voltage sweep)하며 출력 out의 변화를 살피는 매우 단순한 구성이다.

시뮬레이션 도구는 ngSpice다. 그래프 표시기가 내장되어 있어서 손쉽게 결과를 살펴볼 수 있다. 위에서 작성한 테스트벤치를 오픈-소스 SPICE 시뮬레이터 ngSpice로 시험해 보자.

$ ngspice inverter_TB.spice

p와 n 트랜지스터의 채널을 각각 VDD와 VSS에 연결한 회로의 시뮬레이션 결과는 아래와 같다. 디지털 인버터 회로로서 작동되는 모습을 볼 수 있다.

트랜지스터의 채널이 플로팅 된 회로의 시뮬레이션은 다음과 같다. 미세하지만 좀더 많은 전력을 소모하는 것을 볼 수 있다.

VII. 결론

오픈-소스 레이아웃 설계 자동화 도구 Magic을 이용하여 인버터 회로의 그리고 회로를 추출하여 SPICE 시뮬레이션까지 수행하는 예를 보였다. 대상회로는 간단한 디지털 인버터다. Magic 은 상용 도구 못지 않은 계층적 회로 기능을 갖추고 있어서 소규모 라이브러리를 구축하면 레이아웃으로 상당한 규모의 트랜지스터 회로 설계가 가능하다.

"내 칩 MPW"에서 제작해주는 칩의 기본 크기는 1800x1800um 다. 입출력 패드가 차지하는 부분을 제외하면 순수 설계가 들어갈 영역은 950x950um 다. 트랜지스터의 게이트의 최소 길이는 0.5um, 폭은 1um다. 컨택이 차지하는 면적까지 감안 하여 mos 트랜지스터의 단위 면적을 5x5um로 잡더라도 3만여개의 트랜지스터를 넣을 수 있다[(950x950)/(5x5)=36100]. 물론 배선에 필요한 영역을 감안하면 설계 공간은 이보다 훨씬 줄어들지만 1만 트랜지스터 규모의 설계를 구현할 수 있다.

좀더 구체적인 튜토리얼[9]은 물론 입문시 즉시 읽어볼 자료[10][11]들이 있다. Magic의 사용법을 익혀 이보다 더 복잡한 회로를 설계해 보길 바란다. 이번 예제는 간단한 디지털 회로를 그리고 시뮬레이션 하는 예를 보였지만 Magic을 사용하여 아날로그 회로 설계도 가능하다. "내 칩 MPW"에서 제공하는 2P3M 공정은 디지털 회로를 담기에 메탈층의 갯수가 작아 밀집도가 떨어지지만 '아날로그' 회로로에 더욱 어울리는 공정이다. 아날로그와 디지털의 혼합 설계에 도전해 볼 수 있을 것이다. 외국의 경우 재미있는 MPW 프로젝트가 수행되는 것을 본다. 참고자료 [13]을 살펴보기 바란다. 반도체 설계와 칩 제작이 심오한 알고리즘에 묶이지 않고 즐기는 문화가 되면 좋겠다.

레이아웃을 그리면 되지 굳이 회로도를 쳐다보는 이유는 설계 생산성 때문이다. 레이아웃을 편집하는 일은 대단한 수고가 든다. 회로도로 충분히 설계한 후 레이아웃을 단숨에 그리는 편이 설계 생산성에 유리하다. 다음 편은 LVS 를 다룬다.

-------------------------------------------------------------------------------

[참고]

[1] Magic, https://en.wikipedia.org/wiki/Magic_(software)

[2] NSPL PDK, http://mpw.kion.or.kr/info/notice_list.asp

[3] Magic Tech-File Information page, http://opencircuitdesign.com/magic/tech.html

[4] ETRI 0.5um CMOS DK, https://github.com/GoodKook/ETRI-0.5um-CMOS-MPW-Std-Cell-DK

[5] Magic User Guide, http://opencircuitdesign.com/magic/userguide.html

[6] Chip Manufacturing - How are Microchips made? | Infineon, https://youtu.be/bor0qLifjz4?si=_E04jMdSl9d5Mfo5

[7] CMOS Tech: NMOS and PMOS Transistors in CMOS Inverter (3-D View), https://youtu.be/oSrUsM0hoPs?si=TwaiKRg-jpOCOMVk

[8] Low-C ESD Protection Design in CMOS Technology, https://www.intechopen.com/chapters/66524

[9] Analog Layout; Wells, Taps and Guard-rings, https://pulsic.com/analog-layout-wells-taps-and-guard-rings/

[10] Distribution Documentation (PDF format),

ttp://opencircuitdesign.com/magic/magic_docs.html

[11] Reduced Magic Tutorial, https://www.eecg.utoronto.ca/~jzhu/courses/ece435/magic_tutorial.pdf

[12] Introduction to the MAGIC VLSI Design System, https://terpconnect.umd.edu/~newcomb/vlsi/magic_tut/Magic_x3.pdf

[13] Learn ASIC Design, https://www.youtube.com/playlist?list=PLWm3YS7ce87kaG0GkhW9uOMLDRcapD24D

1. Learn ASIC design with the 1-minute MOSFET

2. From top to Transistors: opensource Verilog to ASIC flow

3. Python design of a hardware digital tuner on FPGA and ASIC

4. Python to HDL: full Amaranth walkthrough to FPGA and ASIC GDS

5. The Hidden Power of Formal Methods in Hardware Design: Crash Course

6. TinyTapeout04: demoboard preview and quickstart guide

7. Open Source Analog ASIC design: Entire Process

[14] SILIWIZ, https://app.siliwiz.com/

댓글 없음:

댓글 쓰기