"VLSI 레이아웃 설계 기초"

[8] Std-Cell 제작 실습: DFF-SR

"VLSI 레이아웃 설계 기초"는 "내 칩(My Chip) MPW 서비스": 오픈-소스 도구 활용 반도체 설계 특별과정 중 첫번째 강좌다. 오픈 소스 도구의 기초적인 사용법과 레이아웃 설계와 검증을 정성적으로 다룬다(Quantative approach to VLSI layout design using Open-Source EDA tools).

강의 내용은 아래와 같다.

[1] 리눅스 및 VLSI 레이아웃 도구 설치 [링크]

[2] XSchem, CMOS 인버터 회로도 작성과 시뮬레이션 [링크]

[3] Magic, CMOS 인버터 레이아웃 작성과 회로추출 [링크]

[4] Netgen, 추출한 회로 비교(LVS) [링크]

[5] XSchem 실습: 인버터 회로도 (Schematic Design) [링크]

[6] Magic 실습: 인버터 레이아웃 (Layout Design) [링크]

[7] Netgen 실습: 네트리스트 비교 및 회로 시뮬레이션 [링크]

[8] Std-Cell 제작 실습: DFF-SR [링크]

-----------------------------------------------------------

목차

I. 표준 셀(Standard Cell) 개요

II. 표준 셀(Standard Cell) 그리기 규칙

III. 표준 셀 D-플립 플롭 기능

III-1. D 플립 플롭의 기능 사양

III-2. 회로도 작성

III-3. 시뮬레이션

IV. 표준 셀 D-플립 플롭의 레이아웃

IV-1. 표준 셀 INVX1

IV-2. 표준 셀 NAND2X1

IV-3. 계층적 D 플립-플롭 레이아웃

IV-4. LVS

V. 표준 셀 D-플립 플롭 레이아웃 평가

-----------------------------------------------------------

표준 셀은 IC 설계에서 사용되는 반도체 설계 방법론(특히 디지털)의 일환이다. 모든 설계를 트랜지스터 수준에서 설계 하기에는 너무나 많은 수고가 든다. 이보다 한단계 높은 논리회로 수준에서 설계하는 경우 자동화 도구의 조력을 받을 수 있다. 기본적으로 논리회로는 식(logic expression)으로 표현할 수 있고 수학적으로 알고리즘을 동원하여 최적화 할 수 있다. 뿐만 아니라 배치와 배선의 자동화(Place & Route Automation)를 꾀할 수 있다.

배선(routing)은 부품의 내부 설계에는 간여하지 않고 오직 금속 층을 사용하여 부품사이의 기하학적 연결을 수행한다. 이때 사용될 부품은 자동 배선을 감안하여 크기와 핀의 간격과 같은 기준이 필요하다. 자동 배선 도구는 금속층을 활용하게 되는데 금속층의 두께(width)와 이격거리(separation) 그리고 비아(via)의 그리기 규칙(layout desifn rule)을 따른다.

II. 표준 셀(Standard Cell) 그리기 규칙

"내 칩(My Chip) MPW" 서비스[1]를 통해 제공하는 공정의 사용 가능한 금속층은 3개에 불과하며 금속의 두께와 비아의 크기 그리고 겹친 비아(stacked via) 금지등 제한 규정이 있다. 자동 배선 도구가 이 규정을 따라야 함은 물론이다. 자동화 배선 도구에서 사용 가능하도록 아래와 같이 셀 그리기 규칙을 수립하였다. 표준 셀 사이의 배선 자동화 규칙은 LEF(Library Exchange Format)[10]에 규정되어있다. 경희대학교 디자인 킷은 표준 셀과 자동 배치배선용 LEF를 제공한다[2].

[주] 표준 셀은 RTL 합성과 자동 배치 배선을 위한 것이다. 추상화 수준을 높일 목적이 아니라면 단지 레이아웃 만으로는 아무런 실용적 의미를 갖지 못한다. 경희대학교 디자인 킷[2]은 합성용 리버티(Liberty)와 합성후 네트 시뮬레이션용 베릴로그 모델 그리고 자동배선용 LEF 를 표준 셀과 함께 제공한다.

Liberty*: https://github.com/GoodKook/ETRI-0.5um-CMOS-MPW-Std-Cell-DK/blob/main/digital_ETRI050_m2d/khu_etri05_stdcells.lib

Std-Cell Verilog Model: https://github.com/GoodKook/ETRI-0.5um-CMOS-MPW-Std-Cell-DK/blob/main/digital_ETRI050_m2d/khu_etri05_stdcells.v

LEF: https://github.com/GoodKook/ETRI-0.5um-CMOS-MPW-Std-Cell-DK/blob/main/digital_ETRI050_m2d/etri050_stdcells.lef

[*] 표준셀의 타이밍 자료는 무효다.

1. 금속 층의 활용

금속1 층(metal 1 layer)은 단위 셀 내의 지역 배선(cell internal route)에 사용한다. 자동 배선에서 금속1 층의 사용은 수평 배선에 사용할 수 있으나 극히 제한적이다. 안테나 룰에 민감하다. 금속 2와 3층(metal 1 and metal 3 layer)은 셀 사이의 전역 배선(inter-cell global route)에 활용한다. 금속 2층은 수직(horizontal route), 금속 3층은 수평 배선(vertical route)에 사용한다.

2. 금속 배선의 간격(Pitch or Tracks)

레이아웃 그리기 규칙의 배선용 금속 2와 3층의 두께, 비아의 크기를 감안하여 배선이 지날 경로(track)의 간격은 수평과 수직 공히 3um 로 한다.

3. 표준 셀의 높이

셀의 높이는 자동 배선 도구의 성능에 영향을 받지만 이를 일률적으로 장담하기는 어렵다. 셀을 조밀하게 그릴 경우 배선에 실패할 수 있고 넓게 그릴 경우 유휴공간이 늘어난다. 일반적으로 표준셀은 9 또는 12 트랙(Track)이지만 경희대학교 디자인 킷[2]의 표준 셀은 몇가지 베릴로그 설계를 활용하여 자동 배치와 배선을 시도한 끝에 셀의 높이는 13개 트랙이 지나는 것으로 확정했다.

4. 트랜지스터의 채널 크기

트랜지스터의 채널 크기는 최소 권장 보다 큰 폭 3um, 길이 0.6um 로 하였다.

아래 그림은 실제 배선이 이뤄진 레이아웃의 일부 모습이다. 굵은 사각형은 표준 셀 중 복잡도가 높은 D 플립-플롭 이다. 셀 내부의 지역 배선에서 금속 1층(파란색)이 사용 되었고 그 위로 금속 2(보라색)의 수직 배선, 최상층 금속3(분홍색) 배선이 트랙을 따라 지나고 있다. 큰 정사각형 분홍색은 수직과 수평 배선 사이의 비아2(via2), 보라색 정사각형은 금속1과 2 사이의 비아1(via1)이다.

비아1은 셀의 포트를 전역 배선으로 연결한다. 셀 내부의 배선은 가급적 금속1 만을 사용하지만 피치못할 경우 금속 2를 최소한으로 사용한다. 이때 셀의 포트가 자동 배선에 막히지 않도록 수직 배선으로 만 사용하는 것을 원칙으로 한다.

표준 셀 그리기 규칙을 적용한 D 플립-플롭 표준 셀의 모습은 아래와 같다. 폴리 실리콘 컨택과 디퓨젼 컨택은 비교적 자유롭지만 비아1(via1)은 자동 배선 도구와 보조를 맞춰야 하므로 반드시 트랙 선상에 놓도록 한다.

많은 금속층을 가진 공정의 경우 전역 배선을 할 수 있는 여유가 많고 대부분 겹친 비아를 허용하므로 표준 셀을 조밀하게 그릴 수 있다. 5개 금속층을 가진 SkyWater130[3]의 D-FF(dffbbn1)의 내부 모습은 아래와 같다. 셀 내부가 매우 조밀하게 구성된 것을 알 수 있다.

경희대학교 디자인 킷[2]의 LEF에 규정된 배선 규칙은 다음과 같다. 금속 층의 배선 방법과 비아 뚫기 규칙을 정의한다.

UNITS

DATABASE MICRONS 1000 ;

END UNITS

USEMINSPACING OBS ON ;

USEMINSPACING PIN OFF ;

CLEARANCEMEASURE EUCLIDEAN ;

MANUFACTURINGGRID 0.15 ;

LAYER nwell

TYPE MASTERSLICE ;

END nwell

LAYER nactive

TYPE MASTERSLICE ;

END nactive

LAYER pactive

TYPE MASTERSLICE ;

END pactive

LAYER poly

TYPE MASTERSLICE ;

END poly

LAYER cc

TYPE CUT ;

SPACING 0.9 ;

END cc

LAYER metal1

TYPE ROUTING ;

DIRECTION HORIZONTAL ;

PITCH 3.0 ;

OFFSET 1.5 ;

WIDTH 0.9 ; # ETRI050 Rule: WIDTH=0.8

SPACING 1.05 ; # ETRI050 Rule: SPACING=1.0

RESISTANCE RPERSQ 0.09 ;

CAPACITANCE CPERSQDIST 3.2e-05 ;

END metal1

LAYER via1

TYPE CUT ;

SPACING 0.9 ;

END via1

LAYER metal2

TYPE ROUTING ;

DIRECTION VERTICAL ;

PITCH 3.0 ;

OFFSET 1.5 ;

WIDTH 1.05 ; # ETRI050 Rule: WIDTH=1.0

SPACING 1.05 ; # ETRI050 Rule: SPACING=1.0

RESISTANCE RPERSQ 0.09 ;

CAPACITANCE CPERSQDIST 1.6e-05 ;

END metal2

LAYER via2

TYPE CUT ;

SPACING 0.9 ;

END via2

LAYER metal3

TYPE ROUTING ;

DIRECTION HORIZONTAL ;

PITCH 3.0 ;

OFFSET 1.5 ;

WIDTH 1.2 ; # ETRI050 Rule: WIDTH=1.2

SPACING 1.05 ; # ETRI050 Rule: SPACING=1.0

RESISTANCE RPERSQ 0.05 ;

CAPACITANCE CPERSQDIST 1e-05 ;

END metal3

VIA M2_M1 DEFAULT

LAYER metal1 ;

RECT -1.050 -1.050 1.050 1.050 ;

LAYER via1 ;

RECT -0.450 -0.450 0.450 0.450 ;

LAYER metal2 ;

RECT -1.050 -1.050 1.050 1.050 ;

END M2_M1

VIA M3_M2 DEFAULT

LAYER metal2 ;

RECT -1.050 -1.050 1.050 1.050 ;

LAYER via2 ;

RECT -0.450 -0.450 0.450 0.450 ;

LAYER metal3 ;

RECT -1.050 -1.050 1.050 1.050 ;

END M3_M2

III. 표준 셀 D-플립 플롭 기능

플립 플롭은 디지털 정보의 저장소로서 순차회로의 핵심이다[4]. 표준 논리회로를 활용하여 D 플립플롭을 설계한다.

III-1. D 플립 플롭의 기능 사양

비동기 셋(async. set)과 리셋(async. re-set)을 가진 상승 엣지 트리거(positive-edge trigger) D-형 플립-플롭을 표준 셀로 작성 한다. 잘알려진 TTL 7474의 CMOS 버젼 74HCT74의 내부 회로구성을 차용하여 기능 사양(functional specification)으로 삼았다. 기능도는 아래와 같다.

[그림출처] D-Type Positive-Edge-Triggered Flip-Flops With Clear and Preset[5]

III-2. 회로도 작성(D-FF Schematic)

XSchem으로 기능 사양서에 따라 회로도를 아래와 같이 작성한다. 이번 실습은 회로도와 레이아웃 폴더를 분리하였다. 실습 디렉토리 구조는 아래와 같다.

회로도 작업 폴더로 이동한 후 XSchem 실행.

$ cd ~

$ cd ~/Tutorials/1-4_StdCell_DFFSR/Sch

$ xschem

하위 회로로 NAND2X1과 INVX1를 별도로 작성하여 계층적 회로로 작성 하였다. 트랜지스터의 폭과 길이는 미리 만들어 둔 표준 셀과 동일하게 주었다.

플립-플롭에서 전자정보는 NAND 게이트의 궤환(feed-back)에 의해 유보된다. 이 궤환의 경로에 외부 영향을 배제 하기 위해 D 입력에 반전 버퍼(inverter)를 달았다. 아울러 출력의 궤환작용이 외부에 영향을 주지 않도록 역시 반전 버퍼가 있다. 입력과 출력에 모두 반전 버퍼를 달고 있지만 전역 신호 리셋 R (/CLEAR)과 셋 S (/PRE)은 반전을 상쇄하기 위해 맞바꿨다.

III-3. 시뮬레이션

트랜시언트 시뮬레이션(transient simulation) 결과는 아래와 같다. 비동기 R(/CLR)과 S(/PRE)의 동작과 클럭의 상승 엣지에 동기된 정보보유(latch)의 동작을 확인 하였다.

IV. 표준 셀 D-플립 플롭의 레이아웃

기능이 검증된 D 플립-플롭의 회로도를 사양으로 레이아웃을 그려보자. 회로도에 NAND 와 INV 게이트 그리고 스위치용 p/n-mos 쌍이 사용되었다. 레이아웃 에서도 이에 대응하는 표준 셀을 준비한다.

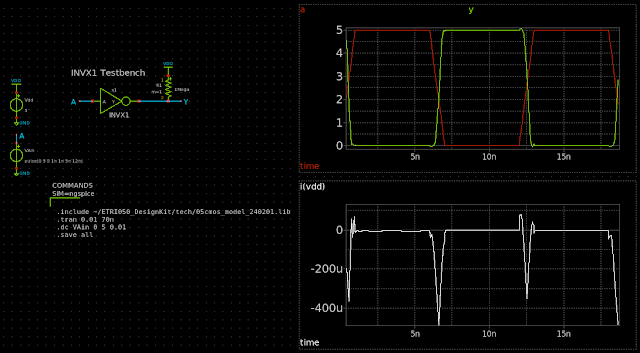

IV-1. 표준 셀 INVX1

INVX1는 구동력(driving power)이 1인 인버터(inverter)다. n-mos의 채널(전자 이동한다)과 p-mos의 채널(홀이 이동한다)은 전하 이동도(mobility)가 2배 차이가 나는 것이 실험적으로 알려져 있다[6]. 이동도가 서로다른 채널을 상보적(complementary)으로 사용하는 CMOS 에서 이를 해결하는 방법으로 p-mos 트랜지스터의 채널 폭을 두배로 늘린다. 집적도에서 손해보는 방법이지만 가장 수월하다.

트랜시언트 시뮬레이션(Transient Simulation)은 수평축이 시간이다. 입력에 대하여 DUT가 반응하는 시간을 평가한다.

전압 증가 시뮬레이션(V-Sweep Simulation)은 수평축이 전압이다. 입력 전압에 대하여 DUT의 최종 출력 전압을 평가한다.

앞의 실습에서 p와 n-mos의 채널 폭이 동일한 인버터의 입력 전압에 대한 출력의 반응(voltage sweep)과 비교해 보자. 반전 하강하는 출력 곡선이 매우 가파르다. n-mos가 빠르게 반응하기 때문이다.

트랜시언트 시뮬레이션으로 비교해 보면 두 인버터 출력의 상승 반전과 하강 반전되는 시간의 차이가 드러난다. 좌측 그래프는 p-mos와 n-mos의 채널 폭이 동일한 경우다. 우측 그래프는 p-mos 채널 폭이 n-mos 채널 폭의 2배인 경우다.

IV-2. 표준 셀 NAND2X1

표준 셀 NAND 게이트의 회로도와 레이아웃은 아래 그림과 같다.

NAND2X1의 트랜시언트 시뮬레이션 결과는 아래와 같다. 두 입력이 모두 p-mos를 켜는 경우 vdd와 출력의 작아져서 반응 시간이 빠르다.

직렬 연결된 두 n-mos가 켜지는 경우 채널 길이(저항)가 두배가 된다. 이를 보상하기 위해 채널 폭을 늘렸다. 두 p-mos는 병렬 연결이다. 둘 중 하나만 켜지는 경우는 직렬연결된 두 n-mos와 균형을 이루지만 모두 켜지는 경우 빠르게 동작한다. 이를 보상하기 위해 n-mos의 채널 폭을 두배로 늘였다. 표준 셀 INVX1, NAND2X1, NOR2X1, SWITCH2X1의 레이아웃을 비교해 보면 트랜지스터의 채널 폭을 달리하는 이유를 같은 논리로 설명할 수 있다.

IV-3. 계층적 D 플립-플롭 레이아웃

미리 구축해 놓은 논리 게이트들의 표준 셀 레이아웃을 활용하여 회로도와 동일한 D-플립 플롭을 그린다.

$ cd ~

$ cd ~/Tutorials/1-4_StdCell_DFFSR/Layout

$ magic -d XR DFFSR74

표준 게이트를 하위회로로 두고 있는 계층적 레이아웃이다. 레이아웃의 이름은 DFFSR74.mag 다.

회로도의 p와 n-mos 쌍의 스위치를 표준 셀로 만들어 하위회로로 활용 하였다.

IV-4. LVS

회로도와 레이아웃의 동일성 검증을 위해 LVS를 실시한다. Magic 레이아웃의 이름은 DFFSR74 이며 회로도의 D 플립-플롭의 이름은 DFFSR 이다. 회로도의 네트리스트는 시뮬레이션을 위해 미리 생성해둔 DFFSR_TB.spice 다. 이 네트리스트 내에 하위회로로 존재하는 DFFSR와 레이아웃에서 추출한 네트리스트의 하위회로 DFFSR74를 비교한다. LVS의 결과 보고서는 LVS_DFFSR74_DFFSR.txt 로 하였다.

"./DFFSR74.spice DFFSR74" \

"../Sch/simulation/DFFSR_TB.spice DFFSR" \

./netgen_setup.tcl LVS_DFFSR74_DFFSR.txt

주] 설계는 도구의 반복 실행이다. 매번 명령줄에서 긴 명령을 입력하려면 피곤하다. 스크립트를 작성해 두도록 한다. 위의 LVS 실행 스크립트는 run_lvs.sh 다.

$ ./run_lvs.sh DFFSR74 DFFSR

LVS 수행 후 결과는 두 회로의 네트리스트 불일치(mismatch)로 판명 되었다. 보고서를 열어 원인을 살펴보자. 처음 발견된 불일치는 NAND2X1의 핀 목록(pin list)에 불일치가 있다고 한다.

Netgen은 NAND2X1의 레이아웃과 회로도의 두 입력 순서가 바뀐 것을 찾아내 이를 불일치 판정했다. NAND 게이트의 논리를 따져보면 두 입력의 순서가 바뀌어도 동작과 무관 하다. 하지만 LVS는 매우 민감하다. 회로 전체를 살펴보고 '오류(error)', '경고(warning)', '통보(notice)' 등을 알려 줄 수 있으면 좋겠지만 Netgen은 그정도 지능(intelligence)은 가지고 있지 않다. 최근 상용 반도체 설계 도구에 인공지능(AI) 넣기가 한창이다. 오픈-소스 도구에도 이의 적용이 멀지 않았다.

이어서 두 네트리스트 사이에 하위회로 구성이 다르다는 점을 지적하고 있다. 회로도에 없는 SWITCH2X1이 레이아웃에 존재한다. Netgen은 하위회로 레이아웃을 상위회로로 평활화(flatten) 하여 등가성을 확인해 준다. 두 회로의 전체 구성(사용된 트랜지스터의 수, 네트의 수)은 일치하지만 네트이 연결에 불일치가 발견 되었다는 보고다.

레이아웃 DFFSR74 회로에서 네트 R이 두개의 NAND게이트 모두 B 포트에 연결되었으나 DFFSR의 회로도에서는 각각 B와 A 포트에 연결되어 있다. 네트 S의 경우 DFFSR74에서는 각각 A와 B에 연결되었지만 DFFSR 회로도는 모두 B 포트에 연결 되었다.

NAND 게이트는 A와 B 포트가 바뀌어도 기능상 등가이지만 LVS의 불일치를 바로 잡도록 하자. 레이아웃을 수정하기 보다 회로도를 수정하는 편이 수월하다. 회로도의 수정은 다음과 같다.

- 하위회로 NAND2X1의 A 와 B를 맞바꾼다.

- 네트 R이 X7의 B에, 네트 S는 X8의 A 에 연결 한다.

회로도 수정 후 LVS를 실시하여 두 네트리스트가 일치하는 결과를 얻었다.

회로도를 수정하였으므로 시뮬레이션을 다시 실시하여 반드시 검증해야함은 물론이다.

V. 표준 셀 D-플립 플롭 레이아웃 평가

설계에 사용될 부품을 규격화 해 놓음으로써 얻는 장점이 있다. 배치와 배선을 수행하는 자동화 도구에 의해 활용되려면 부품의 외형 규격화(standarized footprint)는 필수다. 배선 자동화 도구가 사용할 금속층의 규칙으로 금속2층은 수직배선, 금속 3층은 수평배선으로 규정했다고 하자. 전역 배선 규정은 LEF(Library Exchange Format)에 명시된다. 이 규정으로는 위에서 작성한 DFFSR74는 매우 부적절하다. 셀 내부에 유휴공간이 많고 수평배선으로 금속2가 다수 사용되었기 때문에 전역배선의 공간이 없다.

제대로 그린 표준 셀 DFFSR의 레이아웃은 아래와 같다. 약 32개 가량의 트랜지스터를 포함하는 레이아웃은 하위 셀을 불러오지 않고도 충분히 최적화된 셀을 그릴 수 있다.

표준 셀은 레이아웃 뿐만 아니라 자동 배치와 배선 도구를 위한 정보를 제공해햐 한다. 표준 셀의 크기와 배치시 상하 좌우 뒤집힘(flip)의 가능 여부, 핀(포트)의 금속층 좌표와 입출력 방향 그리고 금속 층별 배선을 금지하는 영역(obstruction)을 정의해 주어야 한다. 자동 배선도구는 셀 내부를 들여다 보지 않는다. 따라서 OBS 영역은 셀 내부에서 사용된 금속층의 영역을 표시하여 배선에 사용하지 못하도록 한다. 표준 셀 DFFSR의 LEF 매크로 정의는 아래와 같다.

MACRO DFFSR

CLASS CORE ;

FOREIGN DFFSR ;

ORIGIN 0.000 0.000 ;

SIZE 69.000 BY 39.000 ;

SYMMETRY X Y ;

SITE core ;

PIN D

DIRECTION INPUT ;

USE SIGNAL ;

PORT

LAYER metal2 ;

RECT 27.900 14.850 29.100 17.100 ;

END

END D

PIN S

DIRECTION INPUT ;

USE SIGNAL ;

.......

END S

......

PIN Q

DIRECTION OUTPUT ;

USE SIGNAL ;

PORT

LAYER metal2 ;

RECT 63.900 15.900 65.100 18.150 ;

END

END Q

PIN vdd

DIRECTION INOUT ;

USE POWER ;

SHAPE ABUTMENT ;

PORT

LAYER metal1 ;

RECT -0.900 37.800 69.900 40.200 ;

END

END vdd

PIN gnd

DIRECTION INOUT ;

USE GROUND ;

SHAPE ABUTMENT ;

PORT

LAYER metal1 ;

RECT -0.900 -1.200 69.900 1.200 ;

END

END gnd

OBS

LAYER metal1 ;

RECT 1.200 30.900 3.000 37.500 ;

RECT 4.200 31.800 6.000 36.900 ;

..........

RECT 66.000 1.500 67.800 5.100 ;

LAYER via1 ;

RECT 30.900 27.300 33.000 29.400 ;

RECT 36.300 28.800 38.400 30.900 ;

.........

LAYER metal2 ;

RECT 15.900 31.800 18.900 33.900 ;

RECT 19.800 31.800 21.900 33.900 ;

.........

END

END DFFSR

오픈-소스 Magic 도구는 레이아웃으로부터 표준 셀의 라이브러리 정보를 추출해준다. 경희대학교 디자인 킷[2]은 레이아웃에서 LEF 정보의 추출과 통합 수정될 경우 두 레이아웃 사이의 네트리스트 비교(LVL, Layout-vs-Layout)등 일련의 표준 셀 구축용 스크립트를 제공한다. 자신만의 최적화된 표준 셀 라이브러리를 구축해 보자.

-------------------------------------------------------------------------------

[1] KION My Chip MPW, http://mpw.kion.or.kr/

[2] 경희대학교 디자인 킷, https://github.com/GoodKook/ETRI-0.5um-CMOS-MPW-Std-Cell-DK

[3] SkyWater130 Process, https://skywater-pdk.readthedocs.io/en/main/rules/assumptions.html

[4] 플립-플롭, https://ko.wikipedia.org/wiki/%ED%94%8C%EB%A6%BD%ED%94%8C%EB%A1%AD

[5] Flip-Flop, https://en.wikipedia.org/wiki/Flip-flop_(electronics)

[6] CDx4HCT74 Dual D-Type Positive-Edge-Triggered Flip-Flops With Clear and Preset, https://www.ti.com/lit/gpn/CD74HCT74

[7] 장효과 트랜지스터, https://ko.wikipedia.org/wiki/%EC%9E%A5%ED%9A%A8%EA%B3%BC_%ED%8A%B8%EB%9E%9C%EC%A7%80%EC%8A%A4%ED%84%B0

[8] Field Effetc Transistor, https://en.wikipedia.org/wiki/Field-effect_transistor

[9] Predicting CMOS Speed with Gate Oxide and Voltage Scaling and Interconnect Loading Effects, https://www.researchgate.net/publication/3063052_Predicting_CMOS_speed_with_gate_oxide_and_voltage_scaling_and_interconnect_loading_effects

[10] LEF/DEF Reference Manual, https://www.ispd.cc/contests/18/lefdefref.pdf

댓글 없음:

댓글 쓰기