"VLSI 레이아웃 설계 기초"

[5] XSchem 실습: 인버터 회로도(Schematic Design)

"VLSI 레이아웃 설계 기초"는 "내 칩(My Chip) MPW 서비스": 오픈-소스 도구 활용 반도체 설계 특별과정 중 첫번째 강좌다. 오픈 소스 도구의 기초적인 사용법과 레이아웃 설계와 검증을 정성적으로 다룬다(Quantative approach to VLSI layout design using Open-Source EDA tools).

강의 내용은 아래와 같다.

[1] 리눅스 및 VLSI 레이아웃 도구 설치 [링크]

[2] XSchem, CMOS 인버터 회로도 작성과 시뮬레이션 [링크]

[3] Magic, CMOS 인버터 레이아웃 작성과 회로추출 [링크]

[4] Netgen, 추출한 회로 비교(LVS) [링크]

[5] XSchem 실습: 인버터 회로도 (Schematic Design) [링크]

[6] Magic 실습: 인버터 레이아웃 (Layout Design) [링크]

[7] Netgen 실습: 네트리스트 비교 및 회로 시뮬레이션 [링크]

[8] Std-Cell 제작 실습: DFF-SR [링크]

----------------------------------------------------------------------------------

목차

I. XSchem: 인버터 회로도

I-1. 작업 폴더

I-2. 회로도 그리기

(1) 심볼 불러오기

(2) 인버터 회로도 작성

(3) 소자의 속성

(4) 입출력 핀 속성

(5) 입출력 핀 순서(핀 번호)

(6) 회로도 저장

I-2. 심볼 그리기

(1) 심볼 그림

(2) 심볼 핀 배치

(3) 핀 번호(순서)

(4) 심볼의 속성 부여

II. 테스트 벤치

(1) 테스트 벤치 작성

(2) 계층적 회로도

III. SPICE 시뮬레이션

(1) 시뮬레이션용 네트리스트 생성

(2) 시뮬레이션 수행

(3) 시뮬레이션 결과 보기

----------------------------------------------------------------------------------

I. XSchem: 인버터 회로도

인버터의 회로도를 작성한다. 재사용을 위해 하위회로(sub-circuit) 형식으로 작성한다. XSchem 도구는 계층화된 회로도 그리기를 할 수 있다.

I-1. 작업 폴더

작업 폴더로 이동,

$ cd

$ mkdir Tutorials/1-1_Inverter_XSchem

$ cd Tutorials/1-1_Inverter_XSchem

실습 폴더구조:

사용 도구:

- XSchem

- Magic

- Netgen

I-2. 회로도 그리기

(1) 심볼 불러오기

인버터 회로에 사용될 소자 nmos4, pmos4의 심볼을 불러온다.

- 단축 키 'Ins' 또는 그리기 바탕에서 마우스 오른쪽 버튼 클릭 후 플로팅 메뉴에서 'Insert symbol' 선택

- 내장 심볼의 위치는 'Home'으로 지정된 디렉토리

(2) 인버터 회로도 작성

회로도를 그리기위해 불러온 소자의 심볼을 재치하고 배선하여 인버터 회로도를 작성한다.

- 두 소자 nmos4 와 pmos4 배치 후 배선

- 배선은 단축키 'w'

- 재사용 가능한 하위 회로(sub-circuit)가 되려면 입출력 핀 심볼을 붙여야 함

(3) 소자의 속성

- 트랜지스터 소자의 속성 값 수정

NSPL 0.5um 공정의 레이아웃 규정에 맞게 트랜지스터 채널의 폭(width)과 길이(length)를 수정한다. 트랜지스터의 모델명을 PDK에서 제공하는 물리 모델명과 일치시킨다. XSchem의 트랜지스터 이름은 pmos, nmos 다. 이를 NSPL의 모델명 nfet, pfet로 수정해 주어야 한다.

(4) 입출력 핀 속성

하위회로(sub-circuit)에서 외부로 노출될 핀(포트) 속성(이름 및 방향)을 지정한다.

- 입출력 핀을 더블 클릭하여 속성(이름) 변경

- 전원은 양방향 핀 심볼 iopin.sym 사용

(5) 입출력 핀 순서(핀 번호)

회로도에 입출력 핀의 순서를 지정한다. 외부 설계 자동화 도구들이 하위 회로를 다룰 때 입출력 포트 매핑(바인딩)시 순서를 따르는 경우를 대비해야 한다. 상위 수준의 설계 도구들, 예를 들어 베릴로그는 이름 매핑(named mapping)을 권장하지만 SPICE의 네트리스트는 하위 회로 연결(배선)시 위치 매핑(positional mapping)만 지원 한다.

편의상 입력, 출력 그리고 전원 핀의 순서를 매겨 두도록 한다. 입출력 핀을 선택 한 후 Shift+S를 눌러 순서를 0번부터 매기도록 한다.

(6) 회로도 저장

- 메뉴: File > Save As

회로도를 저장할 때 파일명이 회로명이 되므로 유의한다.

I-2. 심볼 그리기

(1) 심볼 그림

상위 회로에서 사용될 인버터의 심볼을 그린다. 심볼은 상위 회로에서 표시될 대표 표시(상징)일 뿐 회로 자체와는 관련 없다. 그림을 그리는 도구는 선(line), 원(circle), 문자(text)등을 사용하여 보기 좋게 그린다.

- 메뉴: File > Clear Symbol

메뉴명에 New Symbol이 아닌 Clear Symbol로 되어 있다.

(2) 심볼 핀 배치

심볼 핀(symbol pin)은 하위 회로에서 노출되는 포트다.

- 메뉴: Symbol > Place symbol pin

- 적절한 위치에 하위회로의 입출력 핀을 배치

- 하위 회로의 입출력 핀대응 하도록 심볼에 핀을 배치

- 핀의 이름(name)과 입출력 방향(dir)을 맞춰줄 것

(3) 핀 번호(순서)

하위 회로도의 핀 번호(순서)와 일치 시킨다.

네트리스트를 생성할 때 의 하위 회로(sub-circuit)의 입출력 포트의 위치(순서)에 영향을 준다.

** sch_path: ~/Tutorials/1-1_Inverter_XSchem/inverter.sch

.subckt inverter A Y VP VN

*.ipin A

*.opin Y

*.iopin VP

*.iopin VN

M1 Y A VN VN nfet w=5u l=0.18u m=1

M2 Y A VP VP pfet w=5u l=0.18u m=1

.ends

(4) 심볼의 속성 부여

상징의 역활을 속성에 정의한다. 회로도 바탕을 더블-클릭을 하여 속성 정의 창에 아래와 같이 입력한다.

type=subcircuit

format="@name @pinlist @symname"

template="name=X1"

해당 심볼은 하위회로(subcircuit)를 대표하는 것으로 인스턴스 명(name), 입출력 핀의 목록(pinlist) 그리고 심볼 이름(symname) 등 세가지 속성을 가진다고 명시하고 있다. 심볼의 이름은 하위 회로의 회로도 파일명과 동일하다. inverter.sch의 심볼은 inverter.sym 이다. 아울러 상위회로에서 사례화 되면서 자동으로 이름이 붙도록 문자(insert text)를 추가하였다. @는 변수의 역활을 한다. 심볼 속성에서 name 붙이는 방식을 X1으로 지정되었다. 이 심볼이 사례화 되면 X 문자 뒤로 숫자가 붙는다.

II. 테스트 벤치

(1) 테스트 벤치 작성

시뮬레이션을 위한 테스트 벤치를 작성한다. DUT에 해당하는 'inverter'의 심볼을 불러와 사례화(instantiate) 한다.

(2) 계층적 회로도

사레화 된 심볼을 푸쉬(push)하면 심볼(push symbol) 또는 하위 회로(push schematic)로 내려간다. 하위회로에서 상위 회로로 팝(pop)도 가능하다. 상위 회로도(테스트 벤치)에 하위 회로에 사용된 소자의 모델의 포함되어야 한다. PDK의 모델을 불러오는 경로와 파일명이 지정되었다.

출력에 상당히 큰 용량의 저항을 달아서 전자 회로가 플로팅 되지 않도록 한다.

III. SPICE 시뮬레이션

(1) 시뮬레이션용 네트리스트 생성

오픈-소스 SPICE 시뮬레이션 도구는 ngSpice 다. 회로도는 인간이 읽고 쓰기 좋은 그림이다. 시뮬레이션 소프트웨어는 엄격한 문법체계하에서 표현된 네트리스트를 통해 회로를 이해한다.

검증을 위해 시험 대상 DUT(Design Under Test)이 사례화 되어 있는 테스트 벤치의 네트리스트 추출한다.

생성된 네트리스트에 DUT 회로가 포함된다.

** sch_path: ~/Tutorials/1-1_Inverter_XSchem/inverter_TB.sch

**.subckt inverter_TB

X1 Vin Vout VDD GND inverter

Vdd VDD GND 5

Vin Vin GND 0

R1 VDD Vout 1mega m=1

**** begin user architecture code

* ngspice commands

.include ~/ETRI050_DesignKit/devel/tech/05cmos_model_240201.lib

.dc vin 0 5 0.01

.save all

**** end user architecture code

**.ends

* expanding symbol: ~/Tutorials/1-1_Inverter_XSchem/inverter.sym # of pins=4

** sym_path: ~/Tutorials/1-1_Inverter_XSchem/inverter.sym

** sch_path: ~/Tutorials/1-1_Inverter_XSchem/inverter.sch

.subckt inverter A Y VDD GND

*.ipin A

*.opin Y

*.iopin GND

*.iopin VDD

M1 Y A GND GND nfet w=2.0u l=0.6u m=1

M2 Y A VDD VDD pfet w=2.0u l=0.6u m=1

.ends

.GLOBAL VDD

.GLOBAL GND

.end

DUT를 하위회로로 사례화 한후 입출력 포트를 위치 매핑하고 있다. 계층적 회로 설계에서 다수의 입출력을 갖는 모듈의 포트 매핑의 일관성 유지는 매우 중요하다.

(2) 시뮬레이션 수행

회로도에서 추출한 네트리스트를 읽어 회로 시뮬레이션을 실행한다.

단순한 회로지만 시뮬레이션에 시간이 걸린다.

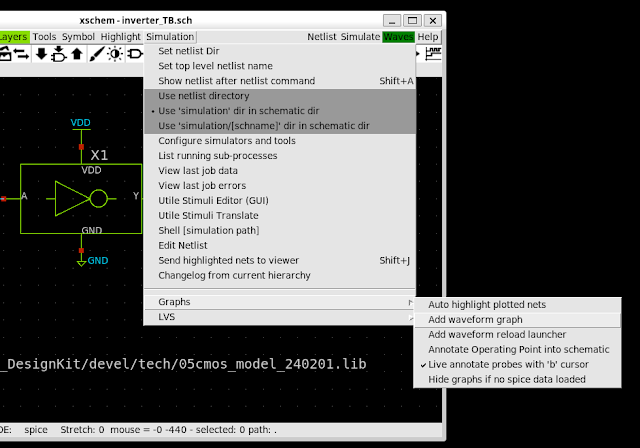

(3) 시뮬레이션 결과 보기

입력 vin의 전압을 점차 증가 시키면서(voltage sweep) 출력을 관찰한다. 회로의 모든 지점에서 회로의 물리량(전압과 전류)를 기록하기 위해 .save all 명령이 사용되었다.

- 파형 보기

- 메뉴: Simulation> Graphs > Add waveform graph

- 관찰할 신호 선택

- 파형 전체보기: 가로와 세로축에 마우스 커서를 위치한 후 'f'

- 전압과 전류 변화 관찰

- 파형에 두개의 커서를 넣을 수 있음('a' 커서와 'b' 커서).

- 'b' 커서를 파형에서 움직이면 해당 값이 실시간으로 회로도에 표시됨

------------------------------------------------------------

II. Magic Layout

<계속>

댓글 없음:

댓글 쓰기