독일의 오픈-소스 도구를 활용한 반도체 설계 인증 교육과정

Development of Certificate Courses and Status Quo of Digital EDA Course using IHP-SG13G2 (C. Wittke)

OpenROAD 프로젝트 사이트(https://theopenroadproject.org/)에 올라온 최근 소식(2024년 9월 30일 현재)으로 독일에 반도체 설계 인증과정을 수립한다고 합니다. 발표 동영상을 보니 "내 칩 MPW"에서도 해볼만 합니다. 세계는 지금 오픈-소스 반도체 설계의 열풍이 불고 있군요.

Kudos to Christian Wittke (IHP) and Thorsten Knoll (HSRM) on their development of a Digital EDA Course using IHP-SG13G2 and OpenROAD ! See the video of Christian's ORConf 2024 talk at https://www.youtube.com/watch?v=Ozd_yXoExLo

IHP는 독일의 공공 연구소로 오픈-소스 PDK 를 개발한다. 자체 크린 룸을 가지고 있으며 MPW 서비스를 제공한다. 디지털 EDA 인증 과정 개발과 현재까지 진행 상황을 발표하겠다.

IHP와 이곳에서 진행하는 프로젝트에 대해서 설명은 이만하고 우리가 준비하고 있는 반도체 인증 교육 프로그램에 대하여 소개한도록 하겠다. 우리의 목표는 반도체 관련 분야의 진보된 교육과 훈련을 제공하는 것이다.

현재 서유럽(독일, 프랑스, 네델란드, 이태리)은 반도체 산업의 일력 부족이 심각하다. 10만여 인력 부족상태다. 2030년까지 13만 명에 이를 것으로 보인다. 향후 10년내 현재 인력들 마저 셋중 한명은 은퇴할 것이다. 과학기술(STEM)을 공부하는 학생들 중 반도체 분야에 전공하려는 숫자가 아주 적은 형편이다.

이에대한 해결책으로 새로운 인력층을 끌어들여야 한다. 대부분 남성 위주에서 여성, 은퇴후 재취업을 원하거나 이직을 고려중인 사람들이 관심을 유도해보려고 한다. 이 산업 분야의 매력을 보여주는 것도 중요하다. 그리고 실질적인 훈련이 되어야 한다.

[주] 반도체 분야가 한때 열풍이 불었던 시절이 있었다. 너도나도 베릴로그니 VHDL을 배우느라 여념이 없었다. 언어만 배워서 할 수 있는 일이란 없다는 것을 깨닳게 되자 흥미를 잃게됐다. 정보산업이 흥하면서 관심이 소프트웨어 개발에 쏠렸다. 범용 컴퓨터와 그래픽 기반 운영체제 상에서 즉시 결과를 보여주는 프로그래밍 언어는 배우는 재미가 있다. 결국 반도체, 특히 전용 반도체 하드웨어 설계 보다 범용 마이크로 프로세서를 활용한 응용 소프트웨어 개발에 치우쳤다. 범용 CPU가 고속화 되면서 전용 반도체 설계는 관심사에서 멀어졌다. 반도체 산업은 경쟁이 심하여 비밀주의와 폐쇄성이 높아지고 반도체 설계 교육은 기초와 이론에 머무를 뿐이었다. 특히 고가의 설계도구(컴파일러 소프트웨어)들은 장벽을 한층 높여 왔고 너무나 넓은 반도체 관련 학과목 간의 추상화 격차도 흥미를 잃게 만드는데 한몫했다. 간단한 인버터 레이아웃을 그리다가 하드웨어 언어로 넘어가더니 급기야 시스템 반도체 설계로 뛰어넘는 지경이다. 결국 학생들은 반도체 설계에서 멀어져만 갔다. 간단한 구문으로 애니메이션을 구현하는 것과 FPGA에 LED 켜보는 것에 드는 노고에 비해 결과로 얻는 흥미의 차이는 자명하지 않은가. 거대시설 산업이라 할 수 있는 소수의 반도체 공장에 비하면 정보산업 계통의 일자리는 넘치고 쉬워 보였을 것다.

정보통신 기술의 근간은 바로 반도체 였다는 점과 실질적인 반도체 산업을 떠받치는 기술에 주목하자. 시스템(CPU와 메모리로 구성되는 컴퓨터) 설계의 출발은 반도체 전자회로(트랜지스터)부터다.

우리의 강좌는 이들 사이의 간극을 좁힐 수 있는 실질적인 교육과 훈련을 제공하겠다. 연구소 및 기업체와 밀접한 협력 관계를 맺고 이들이 필요로하는 인증된 교육과정을 수립한다. IHP는 실제적인 훈련이 되도록 반도체를 설계하고 제작하는 공정시설(크린 룸)을 자체적으로 갖추고 있다.

[주] "내 칩 MPW"는 실질적 반도체 설계 교육에 요구되는 체계를 갖추고 있다. 현재 오픈 PDK로 SkyWater, GF, SG등은 130나노와 180나노 급 공정으로 4~5중 메탈 공정이다. "내 칩 MPW"서비스는 0.5um 공정이긴 하지만 반도체 설계 교육과 훈련에 공정의 선폭이 중요한 것이 아니다. 첨단 공정은 거대 설비에 맞겨두고 교육은 설계에 집중하자.

IHP는 독일 내 여러 관계사들과 협력하여 10여개의 과정을 갖춘 오픈-소스 기반의 2가지 인증교육과정을 준비하고 있는데 공개된 SG13G2 공정을 기반으로 한다.

https://github.com/IHP-GmbH/IHP-Open-PDK

인증과정 1. 디지털 회로 설계

- 반도체 설계 전반을 아우른다.

- 기초 회로(트랜지스터) 설계부터 행위 기술(RTL 합성)까지 다룬다.

- 시뮬레이션과 검증 기법 포함 한다.

- 제조 가능한 GDS 생성 까지.

[주] "내 칩 MPW"공정 표준-셀 디자인 킷은 합성, 자동배치배선, 사인 오프, GDS 생성과정을 모두 학습 할 수 있도록 준비되었다. SPICE, 베릴로그 HDL/VPI, C++/SystemC, FPGA를 활용한 Co-Simulation/Co-Emulation 체계를 갖추고 있다.

인증과정 2. 아날로그/디지털 혼합 신호 설계

- 전과정을 수행해 볼 수 있는 예제

- 디지털 설계와는 다른 단계 추가

[주] "내 칩 MPW" 공정은 '아날로그' 회로 설계가 준비되어 있다. PDK에 BJT(접합 트랜지스터), NMOS, PMOS, DIODE(다이오드), PCAP(컨덴서), PRES(저항) 등 아날로그 회로 설계용 PCELL 들을 제공한다. 조만간 이에 대한 방법도 튜토리얼로 준비할 예정이다.

디지털 설계과정을 소개한다.

오픈-소스 EDA 환경을 기반의 이 교육과정은 아래와 같은 내용을 포함한다.

- 교육과정은 오픈-소스 자체다.

- 교육 자료는 깃(공개 저장소)기반으로 공개한다.

- 칩을 만들기는 오픈-소스 도구들에 맞춰져 있다.

- OpenROAD 도구들과 IHP의 공개 PDK를 활용한다.

- 향후 공개될 더많은 "EDA 마법"들을 익히는데 도움이 될 것이다.

오픈-소스 도구들을 활용하므로써 누구나 칩을 설계 할 수 있게 한다는 것이 목표다. 현재 교육과정은 아래와 같은 절차를 거쳐 수립됐다.

탑-다운 방식:

- 선행 학습사항과 반도체 설계의 전체 과정

- 핵심 학습 부분 도출

- 학습 교재 구성 (교재의 장 구성, 강의와 자습, 실습 및 연습, 질문)

- 학습과정 시험실시 후 의견 수집 및 수정

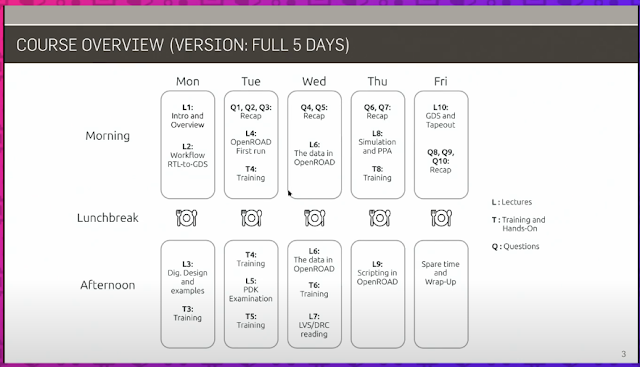

정식과정은 5일간 이뤄지며 칩 설계에 필요한 10개의 강의로 구성됐다. 하루 두강좌이며 중간에 점심시간이 있다. 임원들을 위한 이틀짜리 요약강좌도 있다.

2024년 말까지 강좌안이 수립되면 2025년에 시험실시 될 것이다. 의견은 언재든 환영한다.

2025년 2월 10일부터 5일간 실험적으로 실시된다. 5일 강좌가 유용하지만 필요하다면 2일짜리 출장강좌도 가능하다. 시험 강좌에 참여는 무료다. 향후 정식강좌로 자리하면 유료화 한다. 어떤 문의든 환영한다.

시험 실시되는 강좌에 참여하기 바란다. 프랑크프루트 소재 IHP에 방문하여 공정 시설(크린룸)도 견학 할 수 있다. 위이퍼를 직접 들어보면 남다른 느낌이 들 것이다.

오픈-소스 코뮤니티에 감사한다. 그리고 독일의 공공 자금을 받고 진행하는 다른 오픈 PDK 프로젝트 들도 둘러보시라.

[주] 발표 후 질문 RF 반도체 설계에 대한 질문이 있었다. 이에 대해 아진 준비되지 않았다고 한다.