"내 칩 MPW" NSPL 0.5um CMOS 공정용 표준-셀 디자인 킷 버젼-E 공개

-----------------------------------------------------------------------------

[주의] 이 디자인 킷은 실리콘 검증 되지 않았음. 사용자의 주의를 요함

-----------------------------------------------------------------------------

"내 칩 MPW"의 NSPL 0.5um CMOS/2P3M 공정용 오픈-소스 표준 셀 디자인 킷(경희대학교 DK)이 업-데이트 되었다. 표준-셀이 두가지 버젼으로 발행되었는데 중요 갱신 사항은 아래와 같다.

* NSPL: National Semiconductor Public Laboratory at ETRI

1. 표준-셀 I 형: digital_ETRI050_m1e

- 입출력 포트가 MET1 레이어에 붙어 있어서 배선에 유리하여 밀집도를 더 높게 줄 수 있음.

- 면적 사용량이 약 10% 이상 개선됨

- 적층 비아를 많이 만들어 냄 (FIR_PE 예제의 경우 38개!)

2. 표준-셀 II 형: digital_ETRI050_m2e

- 입출력 포트가 MET2 레이어에 붙어 있어서 상대적으로 MET1를 전역 배선에 사용하기 불리함

- 적층 비아(stacked VIA)를 적게 만들어 냄 (FIR_PE 예제의 경우 8개!)

3. 공통 사항

- 배선 효율이 높아짐(LEF: 표준 셀의 핀/포트 및 OBS 영역 최적화)

- 자동 배선 후 DRC 갯수 감소(LEF: 배선 룰 재정의)

- 내부구조가 지나치게 복잡하여 전역 배선에 불리한 XOR, XNOR, LATCH, TBUF, HAX, FAX 셀을 합성에서 배제 함

* 리버티 파일에서 해당 셀 매크로 정의에 dont_use 옵션 사용

* OR, AND, NOR, NAND, INV 만으로 논리 조합회로 합성

- 표준-셀과 자동 배선기에서 생성된 배선 레이아웃에 대하여 상용 도구와 DRC 교차 검증

4. LEF 변경/최적화

- 표준 셀 배선 금지영역(OBS, obstruction) 및 포트(Pin/Port) 영역 재정의

- 배선 룰 재정의

* metal1: 수직 배선/표준 셀 내부 및 지역배선 용

PITCH=3.0um

Offset=1.5um

WIDTH=0.9um [NSPL Rule: 0.8um]

SPACING=1.05um [NSPL Rule: 1.0um]

* metal2: 수평 배선/전역배선 용

PITCH=3.0um

Offset=1.5um

WIDTH=1.05un [NSPL Rule: 1.0um]

SPACING=1.2um [NSPL Rule: 1.0um (배선 길이가 10um보다 긴 경우 1.2um)]

* metal3: 수직 배선/전역배선 용

PITCH=3.0um

Offset=1.5um

WIDTH=1.2um [NSPL Rule: 1.2um]

SPACING=1.2um [NSPL Rule: 1.0um (배선 길이가 10um보다 긴 경우 1.2um)]

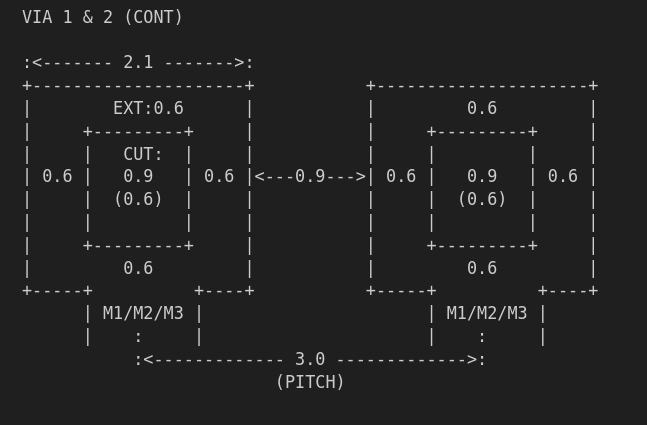

* VIA1 & 2 (CONT)

CUT=0.9um

EXTENSION=0.6um

SIZE=2.1um(=0.6+0.9+0.6)

SPACING=0.9um

디자인 킷 내려받기 깃허브 저장소:

https://github.com/GoodKook/ETRI-0.5um-CMOS-MPW-Std-Cell-DK.git

오픈-소스 내 칩 MPW 튜토리얼:

https://fun-teaching-goodkook.blogspot.com/2024/07/mpw.html

댓글 없음:

댓글 쓰기