ETRI 0.5um CMOS Std-Cell DK 예제: ALU8

목차:

I. 개요

II. 예제 ALU8의 베릴로그 RTL

III. 기능 시뮬레이션(Functional Simulation)

IV. 합성(Synthesis)

V. 자동 배치(Placement)

V-1. GrayWolf: 표준 셀 자동 배치 도구

V-2. 자동 배치 규칙

V-3. 자동 배치의 출력: 배선 전 DEF와 LVS를 위한 SPICE 네트리스트

VI. 자동 배선(Auto-Routing)

VII. 표준셀 병합(Migration)

VIII. 레이아웃 검증: LVS 및 DRC

IX. 입출력 패드 붙이기

X. 마스크용 GDS 생성

XI. 요약

XII. 맺음말

40년 전에도 대규모 집적회로 시스템 설계(VLSI System Design)라는 제목을 가진 수업이 있었다. 반도체 물질과 제조공정으로 시작해서 설계의 예라며 인버터의 모습을 보여줬다. 인버터와 플립플롭으로는 시스템 이라고 하기에는 모자랐던지 계통도와 알고리즘으로 훌쩍 넘어갔다. 중간 과정이 없이 칩 평면 사진을 보여주며 끝내 버리니 궁금증을 넘어 답답함만 쌓인채 과목을 마쳤다.

[이미지 출처] Visual 6502, http://www.visual6502.org/docs/6502_in_action_14_web.pdf

그후 한세대가 지났다. 반도체 설계방법도 눈부시게 발전해서 컴퓨터를 사용한 설계 자동화 도구들과 방법론이 일반화 되었단다. 모눈 종이 위에 그리던 인버터는 이제 화려한 컴퓨터 그래픽 장치 위에서 그릴 수 있게 됐다. 중간 단계도 발전해서 컴퓨팅 언어 기반의 반도체 설계 방법론이 이제 낫설지 않게 됐다. 하지만 화려한 칩 사진 앞에서 그 답답함은 가시지 않는다. 집적회로 교육과정은 인버터 그리기를 넘어 섰을까?

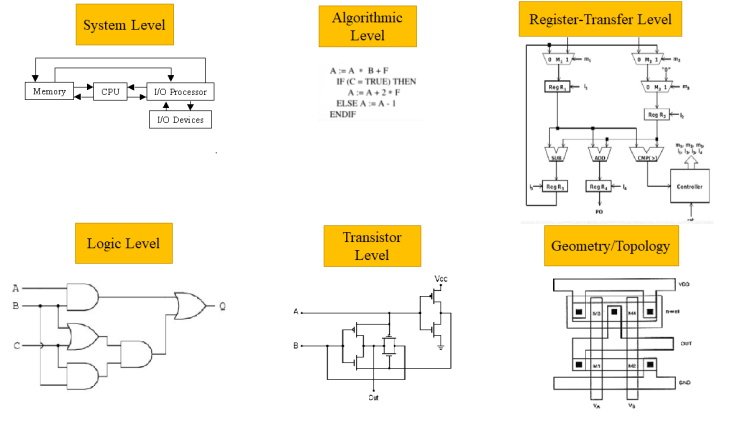

1980년대 초 반도체 설계 방법론을 3가지 측면으로 나눠 봤었다[Gajski–Kuhn chart]. 베릴로그나 VHDL 이라는 반도체 설계 언어조차 표준화 되기 전으로[Hardware Description Language], 컴퓨터를 활용한 반도체 설계(VLSI hardware design) 자동화 시대가 열리기 직전이다. 세 영역 사이를 넘나들며 트랜지스터 회로의 레이아웃 도면으로 세분화 해가는 방법론을 자동화의 큰 과제로 삼았다.

추상화 수준(abstraction level)의 전이에 사용될 자동화 도구들이 등장하면서 각종 용어들이의 개념이 정의 되었다.

컴퓨팅 언어(하드웨어 언어+소프트웨어 언어)기반의 반도체 설계 자동화가 확립된 지금은 위의 Y자 모양 차트가 인용되는 경우는 거의 없지만 각종 용어와 개념들은 여전히 유효하다.

컴퓨터의 가격이 낮아지고 소프트웨어 생산 기술도 발달했다. 높은 비용에 엄두도 못내던 각종 설계 자동화 도구들도 이제 접하기 수월해졌지만 여전히 만만찮은 비용을 요구한다. 다행히 이런 답답함과 고비용의 장벽을 넘어보려는 다수의 노력 덕분에 오픈-소스 반도체 설계도구들이 상당한 수준에 이르럿다. 반도체 제조 공정 또한 학습자(또는 취미가)들에게 개방되고있다[KION My Chip MPW]. FPGA 를 이용해 자신들이 즐기는 장비를 만드는 취미가들의 반도체 설계 능력도 수준급이다[Hermis Lite2 SDR].

예제를 통해 RTL에서 GDS까지 이르는 반도체 설계 전반을 살펴봤다. 표준 셀 기반 주문형 반도체 설계의 전과정에 대한 이해를 높일 수 있는 계기가 되었길 바란다. 반도체 설계 과정을 이해 하는데 빈 구간이 없어졌길 바란다. 반도체 설계 영역에서 사용되는 전문 용어들에 친숙해 졌길 바란다. 두루뭉술하지 않고 구체적이고 실질적인 학습정보가 제공 되었길 바란다.

국가 나노 인프라 협의체 KION의 "내칩(My Chip)" MPW 제작사업의 ETRI 0.5um CMOS 공정용 표준셀 기반 디지털 설계 디자인 킷이 공개되었다[링크]. 예제의 수행은 물론 디자인 킷의 제작에도 오픈-소스 설계도구들을 사용했다. 오픈-소스 도구들은 대중이 함께 발전 시킨 공동의 자산이다. 적극적으로 활용되어 더욱 발전되길 바란다.

오픈 소스 반도체 설계 도구의 의의를 설명한 논문을 인용해 본다.

OpenROAD: Toward a Self-Driving, Open-Source Digital Layout Implementation Tool Chain [link]

"오픈 소스 기획이 성공적으로 이뤄진다면 반도체 설계의 민주화 실현에 일조하는 것이다"

If successful,OpenROAD will help realize the IDEA goal of "democratization of hardware design", by reducing cost, expertise, schedule and risk barriers that confront system designers today.

----------------------------------------------

댓글 없음:

댓글 쓰기