"My Chip MPW Service": Special Course on Semiconductor Design Using Open-Source Tools

This blog is about VLSI design using Open-Source EDA Tools, including SystemC, iVerilog, Yosys, Auto-P&R, NetGen and Magic.

If you're about to begin IC design, Start here;

2023년 8월 31일 목요일

2023년 8월 주간 강좌 및 주간 세미나 결과 보고

2023년 8월 26일 토요일

[Q&A] "내 칩(My Chip)" MPW 관련

[Q&A] "내 칩(My Chip)" MPW 관련

"내 칩(My Chip)" MPW와 관련하여 질문이 있어 아래와 같이 알려 드립니다.

1. 이번 MPW 제작은 과학기술 정통부 주관하는 공모전 입니다. 교내 학사운영(학점 부여, 장학혜택 )과 무관 합니다.

2. MPW 제작 신청을 접수하면 이를 바탕으로 관계 기관의 선정 절차를 거치게 됩니다. 따라서 모든 신청이 칩으로 제작 되지 않습니다.

질문1] 신청할 때 팀을 미리 꾸려야 하는 것인가요? 혼자 신청하면 설계를 신청한 사람들과 같은 한 팀이 되어 설계를 진행하나요?

MPW 제작 신청 시 팀을 꾸리도록 되어 있을 뿐입니다. 신청한 설계가 선정 될 경우 해당 팀원들이 합동으로 설계 또는 개인 별 설계도 무방합니다. 다만, 칩 제작에 제출할 최종 설계 물은 내부 절차(DRC 부합 여부, 시뮬레이션의 정확성)를 거쳐 선정 합니다. 신청서의 대표 학생은 해당 설계에 관한 연락 임무를 받게 됩니다.

질문2] 참여자에게 "독립 심화 학습 " 3학점으로 인정이 되는 것인가요?

그렇지 않습니다. MPW 제작은 교내 학사 운영과 무관한 외부 공모입니다. "독립 심화 학습"으로 학점을 받으려면 이미 공지된 대로 수강 신청을 했어야 합니다. 이번 학기 "독립 심화 학습" 학점 신청은 마감 되었습니다.

질문3] "컴퓨터 구조" 수업은 들었지만 "VLSI 설계"를 수강하지 않아도 괜찮을까요?

신청서의 연계 학과목은 이번 MPW와 연계된 수업 과정이 우리 학교 내에 개설 되어 있다는 뜻입니다. 이를 선수 과목으로 이수해야 하는 조건은 아닙니다.해당 과목의 수강하지 않고도 설계를 할 수 있다면 능력자 입니다. 능력을 보여 주세요.

질문4] 한 학기 동안 설계하는 것인가요?

MPW 제작은 외부 공모이며 학사 일정과는 무관 합니다. 11월 중순에 예정된 설계물 제출 시한 전까지 완료해야 합니다.

질문5] 관련 이론이나 수업을 따로 진행하나요? 아니면 개인이나 팀이 처음부터 따로 공부해서 진행하는 것인가요?

관련 수업은 따로 없습니다. 반도체 전공 트랙에서 매주 반도체 설계에 관한 세미나와 강좌를 개최할 것이므로 참여 하고 질문 하십시요. 세부 학습은 학생의 역량에 달렸습니다. 자율적으로 참여 하십시요.

질문6] 이번 신청 접수에 명단을 올리지 않았더라도 MPW 제작에 참여 할 수 있습니까?

없습니다. 모든 학생의 무질서한 요구를 모두 수용 할 수 없기 때문 입니다. MPW 제작 의사가 있고 이를 성실히 수행하겠다는 약속을 해야 합니다.

질문7] "독립 심화 학습"을 신청한 경우 MPW 제작에 선정되지 않았더라도 학점이 부여 되나요?

"독립 심화 학습"의 학점과 MPW 제작 여부는 별개 사항 입니다. 모든 MPW 제작 신청이 선정으로 이어지지 않습니다. MPW 제작과 학사 운영이 별개로 진행 되는 이유 입니다. "독립 심화 학습"을 신청한 학습 조는 자신들이 제출한 학습 계획에 맞게 결과를 도출 해야 하며 공지된 요구에 부합할 경우에 학점이 부여 됩니다.

질문8] MPW 신청 접수 시 개별 아이디어를 지원 할 수 있습니까?

개별 아이디어를 원할 경우 8월 30일 MPW 접수 설명 세미나 전까지 신청서를 작성해 와서 승인을 받도록 하십시요.

질문9] 아날로그 회로를 설계하고 싶습니다.

30일에 열리는 세미나에서 행할 MPW 제작 지원의 설명과 접수는 디지털 회로에 한 합니다. 아날로그 회로의 경우 이종욱 교수님께 문의 하십시요.

추가 문의는 아래 e-mail을 통하십시요.

국일호 (goodkook@khu.ac.kr)

[주간 세미나 공지] "내 칩(My Chip)" MPW 신청자 최종 모집 (2023년 8월 30일)

[주간 세미나 공지] "내 칩(My Chip)" MPW 신청자 최종 모집 (2023년 8월 30일)

날자: 2023년 8월 30일

장소: 전자정보 대학관 211-2호

내용:

2023년 1차 "내 칩(My Chip)" MPW의 신청 마감일이 8월 31일로 다가옴에 따라 신청 내용과 신청서 작성을 설명 합니다. MPW에 참여하고자 하는 학생은 이번 세미나에 꼭 참석해서 신청서 작성을 마쳐야 마감일 전에 접수 할 수 있습니다.

이번 MPW에 신청 예정인 설계는 총 6개의 설계 입니다.

1. CMOS 공정의 디지털 회로 합성용 표준 셀 라이브러리

2. 바렐 쉬프터 Signed-Digit 곱셈 및 누산기(Multiplier-Accumulator) 설계

3. 8-bit CPU의 범용 산술논리 연산장치(ALU) 설계

4. 부스 알고리즘 8비트 곱셈기(Booth Multiplier) 설계

5. 8비트 CPU 6502 구현

6. 8비트 CPU Z80 구현

1) 이번 MPW의 칩 크기가 1000x1000um 에 불과하여 큰 설계를 넣을 수 없습니다.

2) 따라서 위 설계 중 1~4 항목 중 하나를 선택한 학생을 모아 팀을 만들어 신청 합니다.

3) 설계 5, 6은 공정 단계에서 큰 설계가 반영될 경우를 대비해 신청하려는 것입니다. 둘 중 하나를 선택 하십시요.

4) 중복 선택 가능하며 수요일 세미나 시간에 조정 하도록 합니다.

5) 위의 설계 이외에 다른 설계를 원할 경우 준비해오면 논의하여 접수토록 합니다.

주2] 신청 접수할 개별 설계마다 참여할 구성원은 모두 각자(또는 협력으로) 해당 내용으로 설계하고 가장 우수한(DRC 문제가 없고 시뮬레이션 결과가 적절히 이뤄진) 설계물을 제출 할 것입니다.

주3] 신청한 설계가 모두 선정 된다는 보장은 없습니다(접수 건수에 따라 변경 됨). 향후 MPW 는 매월 계속 될 예정이라고 하니 다음 차수를 위해 준비 되도록 설계를 진행 합니다.

주4] MPW 참여는 "심화학습"의 신청 학점과 무관 합니다. "심화학습" 학점 신청자들은 신청한 내용대로 학습을 진행 하십시요.

2023년 8월 21일 월요일

[반도체 전공 트랙의 주간강좌와 세미나는 열린 공간입니다]

[반도체 전공 트랙의 주간강좌와 세미나는 열린 공간입니다]

1. 주간 강좌와 세미나는 학점 교과목이 아닙니다.

2. 반도체 설계에 관심이 있다면 누구나 참여할 수 있습니다.

3. 강좌와 세미나 시간 불참에 미안해 할 이유가 없습니다.

4. 학습 및 실습 사항은 게시판에 계속 공지될 것입니다. 자율적으로 참여 하십시요.

5. 실습 중 어려움이 있거나 궁금한 점은 언제든 문의 하십시요.

6. 주간강좌 및 세미나 계획(안) 참조 하십시요. [링크]

개방형 온-라인 대중 교육(MOOC)에서 성공 하는 법 [링크]

2023년 8월 18일 금요일

[주간 세미나/강좌 공지] "Verilog RTL 에서 레이아웃 GDS 까지" (2023년 8월 24일)

[주간 세미나/강좌 공지] "Verilog RTL 에서 레이아웃 GDS 까지" (2023년 8월 24일)

[주1] 8월 23일(수)로 예정된 강좌는 MPW 관련 공정측과 회의가 예정되어 있어서 24일(목)로 변경 합니다. 장소와 시간은 추후 변경 될 수 있음.

[주2] 매주 수요일에 실시하던 주간 세미나/강좌는 9월 부터 일정이 변경될 예정 입니다.

[주간 강좌/세미나]

일시: 8월 24일

시간: 오전 10시 30분

장소: (추후공지)

내용:

표준 셀 기반 디지털 반도체 회로 설계의 후반 부 자동화 도구 리뷰

Project_6502 예제의 합성 후 Co-Simulation 실시 방법

예제 실습: "Verilog RTL에서 GDS 레이아웃 까지"[4/4]

Project_6502 예제의 합성 후 Co-Simulation 실시 방법

SystemC/C++로 작성된 높은 시스템 수준의 검증 환경(테스트 벤치)을 구축하여 합성 가능한 6502 CPU의 RTL Verilog 설계를 검증했다.

이 검증 환경은 RTL 설계물이 합성을 통해 더 낮은 수준으로 전환된 후 추출된 네트 리스트 Verilog의 검증에 동일하게 적용 한다. 추상화 수준의 전이 과정에서 발생할 어떤 오류, 설계도구의 오류는 물론 인간 간여 오류에도 충분히 대처하기 위함이다. 특히 합성부터 후반부 작업단계에서 오픈 소스 도구의 사용 이라는 불안을 덜어낼 수 있다는 점에서 그 필요성과 중요성이 있다.

목차

2. 윈도우즈와 리눅스 파일 시스템 교차 접근 방법

3. 합성 후 표준 셀 네트 리스트 파일 생성

3-1. RTL Verilog 파일의 심볼릭 링크

3-2. 합성에서 레이아웃 까지 자동화

3-3. 후 검증

3-4. 클럭 버퍼 처리

-----------------------------------------------------------------------------------------

1. 원 설계물의 항상성 유지

검증을 마친 RTL의 설계물을 전자회로로 전환되는 과정은 합성, 자동배치, 자동배선 등 자동화 변환 도구(design automation tools)에 전적으로 의존하게 된다. 이에 자동화 도구의 신뢰성이 매우 중요하다. 더블어 자동화 도구를 사용하면서 최적화를 위해 또는 도구의 사용조건에 따라 원 설계물에 수정이 가해질 수 있다. 아주 작은 수정이더라도 간과해서는 않되며 끊임없이 검증 되어야 한다. 이에 지켜야 할 기준으로 테스트 환경의 변경은 허용되지 않아야 함은 물론이며 원 설계물이 임의로 복사 편집되지 않도록 관리 되어야 한다.

설계과정에서 생산성 높은 도구의 사용은 설계시간의 단축 뿐만 아니라 재귀적 반복으로 인한 작업자의 피로도 상승에 따른 오류 개입을 피할 매우 중요한 요소다. 윈도우즈의 문서 편집기는 리눅스의 그것보다 매우 직관적며 편이성 또한 높다. SystemC와 C++ 언어를 이용한 테스트 벤치의 제작도구로 사용할 Visual Studio의 생산성(특히 소프트웨어 디버깅)이 매우 높다.

우리가 정립할 설계과정(design flow)에서 C++ 컴파일러 Visual Studio와 HDL 시뮬레이터 QuestaSim은 윈도우즈 체제에서 운용되며 합성 및 배치배선 도구들은 리눅스 체제에서 운용된다. 서로 다른 운영체제의 설계 파일들을 상호 교차접근하기 위해서 파일 시스템이 고려되어야 한다. 다행히 WSL(Windows Subsystem for Linux)는 윈도우즈와 리눅스사이의 응용 소프트웨어 수준에서 자유로운 파일 탐색을 허용한다. 파일경로 분리자(delimiter)의 상이함을 제외하면 실볼릭 링크(symbolic link)와 바로가기(short-cut)를 통해 두 운영체제의 파일 시스템 사이에 상호 교차접근이 가능하다.

2. 윈도우즈와 리눅스 파일 시스템 교차 접근 방법

윈도우즈와 리눅스의 파일 체계는 호환성이 없다. 하지만 WSL을 통해 설치된 리눅스와 윈도우즈 사이에 파일의 상호 접근이 허용된다. 윈도우즈는 WSL의 리눅스 디스크를 네트워크 소켓으로 접근 할 수 있다. 파일 경로는 아래와 같다.

\\wsl.localhost\Ubuntu-20.04

윈도우즈 응용 프로그램 수준에서 리눅스 파일 접근이 가능하여 윈도우즈 파일 탐색기(Explorer)로 접근 할 수 있다.

따라서 윈도우즈의 바로가기(short-cut)로 리눅스 파일을 지정 열람이 가능하다.

리눅스 파일 시스템에도 윈도우즈의 '바로가기'에 해당하는 리눅스의 기능이 있다. 심볼릭 링크(symbolic link)다. 심볼릭 링크를 만드는 명령은 아래와 같다.

$ ln -s <source file path/name> <target file name>

WSL으로 설치된 리눅스에서 윈도우즈의 파일을 심볼릭 링크 할 수 있다. 예를 들어 다음과 같다. 윈도우즈 파일을,

D:\home\Project_6502\Apple2_Co-Sim\Arlet_Verilog-6502_1_Async\ALU.v

리눅스 로컬 폴더의 ALU.v 로 심볼릭 링크 하면 아래와 같다.

리눅스의 입장에서 윈도우즈의 하드디스크는 /mnt 에 장착(mount)되어 있다. 운영체제는 모든 자원(디스크와 파일 뿐만 아니라 입출력 장치들 모두)을 파일의 개념으로 관리한다는 점도 기억해 두자. 위의 예는 윈도우즈 하드디스크 D: 가 /mnt/d 에 장착 되어 있다는 뜻이다.

윈도우즈와 리눅스의 가장 큰 외형상 차이는 경로명 분리자(delimiter)다. 리눅스는 슬러쉬 '/', 윈도우즈는 백-슬러쉬 '\' 다. 상호 교차 링크를 걸 때 이 차이가 귀찮다. 한때 이 문제를 고치려 했으나 윈도우즈가 예전 DOS 시절부터 사용하던 커맨드 라인에 대한 호환성을 유지해야 하므로 어쩔수 없다고 하니 참고 써야한다.

3. 합성 후 표준 셀 네트 리스트 파일 생성

Yosys는 오픈 소스 Verilog 합성(synthesis) 도구다. 이 합성기를 거쳐 생성된 표준 셀(standard cell) 네트리스트를 Verilog로 추출하여 앞서 RTL 검증에 사용했던 테스트 환경에 적용하여 합성기의 기능을 확인하자. 이 과정을 네트 시뮬레이션 혹은 합성 후 시뮬레이션(Post-Synthesis)이라고 한다. 표준 셀의 모델은 목표 반도체 공정에서 제공하는 PDK에 포함되어 있다. 합성 후 네트리스트의 시뮬레이션에 RTL 검증에 사용했던 것과 동일한 테스트 환경을 적용함으로써 오픈 소스 합성기의 신뢰성을 담보할 수 있을 것이다. 합성 후 표준 셀 네트리스트 생성 절차는 아래와 같다.

3-1. RTL Verilog 파일의 심볼릭 링크

합성을 위한 준비는 리눅스 작업 폴더에 RTL Verilog 파일을 심볼릭 링크 시킨다. 합성할 파일들을 넣어둘 source 폴더 를 만든다.

$ ln -s /mnt/d/Verilog-6502_1_Async/ALU.v ALU.v

$ ln -s /mnt/d/Verilog-6502_1_Async/cpu.v cpu.v

3-2. 합성에서 레이아웃 까지 자동화

오픈 소스 툴 qflow 에서 합성을 실시한다. 공정을 osu050 (0.5u 2Poly/3Metal)으로 놓았다. 리눅스의 합성도구는 심볼릭 링크한 윈도우즈 파일을 중단 없이 읽어 들인다.

배선을 원할히 하기 위해 다소 느슨한 density=0.3 로 놓고 배치를 실시한다.

배선이 완료되면 이어서 DRC, LVS, GDS 생성까지 진행 시킨다.

최종적으로 표준 셀까지 모두 합쳐진 레이아웃을 얻는다.

3-3. 후 검증

합성에서 레이아웃을 얻을 때까지 과정은 자동화 툴의 몫이다. 최적의 결과를 얻기 위한 옵션 조정 외 설계자가 간여할 여지는 없다. 설계 자동화 도구도 응용 소프트웨어인 만큼 무조건 신뢰하기 전에 그 결과물을 검증할 필요가 있다. 아울러 설계의 최종 결과물은 전자회로라는 점을 감안 하여 논리적 기능 뿐만 아니라 물리적 특성도 검토되어야 한다. 회로의 시간지연으로 인한 글리치 발생과 클럭과의 셋업 오류는 매우 중요하게 다뤄져야 한다.

자동화 단계를 거칠 때 마다 작업 결과를 검증하기 위한 목적의 네트리스트를 Verilog 파일로 생성한다. 이를 RTL 설계 검증의 테스트 벤치에 동일하게 적용하여 오픈 소스 자동화 툴의 신뢰도를 확인 해 보기로 한다. 합성과 배치배선이 완료되면 synthesis 폴더에 다수의 베릴로그 파일이 존재한다. 그중 합성과 최적화에서 얻어진 cpu.v 와 배선 후 얻은 cpu_postroute.v 를 가지고 시뮬레이션을 실시한다.

합성과 자동 배치배선의 결과로 얻어진 Verilog 파일은 읽기가 가능한 보통의 문서다. 표준 셀라이브러리들을 하위 모듈로 둔 계층화된 구조적 모델이다. 표준 셀 하위 모듈을 부품으로 두고 상호 연결만으로 표현되어 있다. 이를 HDL 시뮬레이션 하려면 하위 모듈들의 행동을 표현한 Verilog가 제공되어야 하는데 공정의 PDK에 포함되어 있다. 위에서 사용한 자동화 도구 qflow의 공정별 PDK를 모아둔 곳은 /usr/local/share/qflow/tech/ 다. 예제의 합성에 사용한 공정은 osu050이다. 합성 후 검증에 필요한 Verilog 파일은 아래와 같다.

검증은 RTL C-Simulation의 테스트 벤치를 그대로 사용한다.

QuestaSim의 do 스크립트에서 Verilog 부분만 수정하면 아래와 같다.

# MTI simulation scrips for

# Arlet's Verilog-6502

# Vendor: GoodKook

# Associated Filename: compile_syn.do

# Purpose: SystemC testbench

# Revision History: 23 Jul 2023

#*************************************************

onbreak {resume}

# create library

if [file exists work] {

vdel -all

}

vlib work

vlog -reportprogress 300 -work work \

#sccom -reportprogress -g -work work ../sc_mem.cpp \

sccom -reportprogress -g -work work ../sc_mem.cpp \

sccom -reportprogress -g -work work ../sc_CPU6502.cpp \

sccom -reportprogress -g -work work ../Apple2.cpp \

sccom -link -lcomdlg32

------------------------------------------------------------------------------

합성후 생성된 cpu.v 에 수정 사항이 있다.

output [15:0] AB,

input [7:0] DI,

output [7:0] DO,

input IRQ,

input NMI,

input RDY,

output WE,

input clk,

input reset

);

시뮬레이션 스크립트는 RTL 때와 다를바 없다.

# MTI compile scrips

# Vendor: GoodKook

# Associated Filename: simulate.do

# Purpose: SystemC testbench

# Revision History: 24 Jul 2023

#***********************************************

vsim -voptargs=+acc work.sc_main -t ps

단, 시간 해상도 지정이 피코 초(-t ps, pico-second)다. 표준 셀 라이브러리의 Verilog 모델에 지간 지연을 포함하고 있다. 보통 RTL 시뮬레이션의 시간 해상도는 나노 초(ns, nano-secod)이나 물리적 특성을 다루는 후반부 시뮬레이션에서는 게이트 통과 지연을 반영한 글리치(glitch)를 표현 하므로 해상도는 이보다 세밀한 피코-초(ps, pico-second)다.

디지털 회로의 물리적인 시간지연을 감안 하지 않고 논리적 행동만을 다룰때 펑셔널 시뮬레이션(functional simulation) 또는 전단 시뮬레이션(Pre-Simulation)이라 한다. 합성 이후 실제 공정의 물리적 정보를 포함하기 시작한 후반 시뮬레이션을 타이밍 시뮬레이션(Timing Simulation), 또는 포스트 시뮬레이션(Post-Simulation)이라 한다.

3-4. 클럭 버퍼 처리

6502 CPU를 검증하기 위한 입출력 장치 구동 소프트웨어 "Apple2_Screen"을 먼저 실행 시킨다. 이어 Verilog 타이밍 시뮬레이션을 진행하자.

run 30 us

안타깝게도 오류를 일으킨다.

원인은 셋업(set-up)과 홀드(hold) 바이얼레이션(violation)이다. 틀어진 클럭(clock skew)으로 인해 디지털 회로 플립-플롭이 오동작 했음을 의미한다. QuestaSim의 데이터 플로우(data-flow) 기능은 오류가 처음 시작된 위치를 추적하는데 도움을 준다.

클럭 신호는 칩 전체에 분포한 플립-플롭 회로들을 작동시킨다. 매우 강력한 구동 능력을 가져야 하므로 특별히 취급 되어야 한다. 큰 구동을 위해 CLKBUF1 이라는 구동 셀(driver cell)이 추가 되어 있으나 그 능력이 모자란 것으로 보인다. 합성기는 클럭 신호에 11개의 클럭 버퍼 CLKBUF1을 삽입하였다. PDK의 셀 라이브러리의 타이밍 모델에 다르면 이 버퍼는 만만치 않은 지연을 가지고 있다.

input A ;

output Y ;

buf (Y, A);

specify

// delay parameters

specparam

tpllh$A$Y = 0.25:0.25:0.25,

tphhl$A$Y = 0.26:0.26:0.26;

// path delays

(A *> Y) = (tpllh$A$Y, tphhl$A$Y);

endspecify

endmodule

이 문제는 추후 해결 하기로 하고 먼저 합성의 기능적 문제만을 따져보기 위해 네트리스트 cpu.v 를 수정하자. QuestaSim의 Dataflow을 통해 찾아낸 클럭 버퍼의 인스턴스 이름은 CLKBUF1_insertXX이었다. 11개의 버퍼를 코멘트 처리하고,

2336: //.Y(clk_bF$buf0)

2337: //);

2338: //

..........................

2378: //

2379: //CLKBUF1 CLKBUF1_insert25 (

2380: //.A(clk),

2381: //.Y(clk_bF$buf9)

2382: //);

2383: //

2384: //CLKBUF1 CLKBUF1_insert24 (

2385: //.A(clk),

2386: //.Y(clk_bF$buf10)

2387: //);

2388:

시간 지연이 없는 버퍼로 대체해 넣는다.

수정된 cpu.v 를 재 컴파일 하여 시뮬레이션을 수행하면 펑션 시뮬레이션과 동일하게 작동 되는 모습을 볼 수 있다.

파형을 관찰 하면 표준 셀의 통과 지연이 반영되고 있는 모습을 볼 수 있다. 클럭 구동의 문제가 있지만 오픈 소스 합성기 yosys 는 기능상 문제없다. cpu_postroute.v 에 대하여 동일한 시뮬레이션을 진행하여 자동 배치배선 기능을 확인해보자.

--------------------------------------------------

[참고]

1. Digital System에서 Setup/Hold, http://www.internex.co.kr/insiter.php?design_file=notice_v.php&article_num=13&PB_1247810668=3

2. 16 Ways to Fix Setup and Hold Time Violations, https://www.edn.com/ways-to-solve-the-setup-and-hold-time-violation-in-digital-logic/

---------------------------------------------------------------------

[이전] Project_6502 예제의 기능적 Co-Simulation 실시 방법

[처음] SystemC 및 SDL2 라이브러리 빌드 하는 방법

2023년 8월 17일 목요일

Project_6502 예제의 기능적 Co-Simulation 실시 방법

예제 실습: "Verilog RTL에서 GDS 레이아웃 까지"[3/4]

Project_6502 예제의 기능적 Co-Simulation 실시 방법

SystemC/C++로 작성된 검증 환경(테스트 벤치)의 목적은 합성 가능한 RTL의 Verilog 설계물을 검증하기 위한 것이다. 검증 환경의 구축에 C++를 동원한 높은 수준의 컴퓨팅언어를 사용하는 이유는 실제와 동일한 환경을 마련하기 위함이다. 추상성이 낮은 HDL 테스트 벤치로는 검증에 사용할 테스트 입력이 단순화 될 수 밖에 없다.

CPU를 설계하여 그를 검증하기 위한 가장 적절한 환경은 규모가 작더라도 입출력 장치를 갖춘 컴퓨터다. 앞서 구성한 SystemC/C++ 검증 환경은 6502 CPU를 사용하는 컴퓨터다.

CPU가 운용하게 될 메모리와 입출력 장치(키보드와 스크린)를 높은 추상화 수준에서 구축하였다.

아울러 CPU가 채택된 소규모 컴퓨터에서 실행 될 펌웨어(모니터 프로그램)을 적용해야 하는데, Apple-1 이 처음 발매 되었을 때 사용되었던 Wozniak[Link]의 모니터 롬 파일을 적재 시켰다. Co-Simulation으로 Apple-1의 모니터 프로그램 사용자 메뉴얼[Link]에 따라 작동 시킴으로써 6502 CPU의 RTL을 검증 하였다.

참고:

1. Steve Wozniak, https://en.wikipedia.org/wiki/Steve_Wozniak

2. Apple-1 Operation Manual, https://archive.org/details/Apple-1_Operation_Manual_1976_Apple_a

목차:

2. 컴파일 스크립트

3. 시뮬레이션 스크립트

4. Co-Simulation 실행

-----------------------------------------------------------------------------------------

1. QuestaSim

가장 믿을 만한 HDL 시뮬레이터로 VHDL, Verilog, SystemVerilog 뿐만 아니라 SystemC 를 지원한다. 이를 위해 GCC/G++ 를 내장하고 있다. 매우 고가의 시뮬레이터 이나 인텔 FPGA 툴과 함께 1년단위 라이센스를 무료로 배포하고 있다. 매우 고마운 일이 아닐 수 없다. QuestaSim의 설치는 아래 링크를 참조하자.

https://fun-teaching-goodkook.blogspot.com/2023/07/questasimmodelsim.html

최정상 도구인 만큼 다양한 기능을 가지고 있고 사용자 매뉴얼이 2천여 쪽에 달한다. 외국어 공부할 때 사전을 다 외우지 않듯이 필요할 때 마다 찾아보기로 하자. 기능이 많다고 사용법이 어려운 것은 아니다. 매우 쉽다. 사용법을 보고 싶다면 아래 링크의 문서를 참조하라.

http://www.ednc.com/wp/wp-content/uploads/2015/06/Questa_10.3d_tutorial.pdf

2. 컴파일 스크립트

베릴로그 파일을 시뮬레이션하려면 컴파일해야 한다. 추후 합성 과정을 거치면 컴퓨팅 언어에서 전자회로의 네트리스트로 바뀌기 전까지는 베릴로그도 컴퓨팅 언어이다. 컴퓨팅 언어로 묘사된 전자회로가 작동하는 모습을 관찰하는 것을 시뮬레이션이라고 한다. QuestaSim에서 Verilog의 컴파일 명령은 vlog 다.

vlog <verilog filename>

수많은 옵션이 따라 붙지만 어쨌든 명령은 한개다. 컴파일 하면서 생성되는 중간 파일과 그 결과 파일은 모두 현재 작업 폴더에서 하위 폴더에 저장 되는데 이 폴더 명은 work 로 지정되어 있다. 따라서 컴파일 하기전에 work 라는 이름의 하위 폴더를 만든다.

vlib work

앞서 VusialStudio로 SystemC와 C++의 소스 파일을 컴파일 했었다. 그때 생성되었던 실행 파일은 QuestaSim에서 사용 할 수 없다. 다행히도 QuestaSim에 GCC/G++를 내장하고 있어서 테스트 환경으로 사용했던 C++ 소스를 변경 없이 컴파일 할 수 있다. SystemC 컴파일 명령은 sccom 이다.

sccom <c/cpp filename>

복수의 소스 파일을 컴파일 해야한다. 개발 중에 수없이 많은 컴파일을 반복 수행해야 한다. 그때마다 일일이 명령줄에서 입력하려면 여간 피곤한 일이 아닐 수 없다. QuestaSim 은 Tcl/Tk 스크립트를 쓸 수 있지만 아주 단순한 자체 스크립트 형식을 가지고 있다. 사실 배치 파일 형식이라 커맨드 라인 입력을 나열해 놓은 것에 불과하다. Do 스크립트라고 하는데 파일 확장자가 .do 다. Project_6502 예제의 스크립트는 TB/MTI 폴더에 있다.

그 중 한 스크립트를 보자.

# filename: Apple2_Co-Sim\TB\MTI_1_Async\compile.do

# MTI simulation scrips for

# Arlet's Verilog-6502

# Vendor: GoodKook

# Purpose: SystemC testbench

# Revision History: 23 Jul 2023

#****************************************************************

onbreak {resume}

# create library

if [file exists work] {

vdel -all

}

vlib work

vlog -reportprogress 300 -work work ../../Arlet_Verilog-6502_1_Async/ALU.v

vlog -reportprogress 300 -work work ../../Arlet_Verilog-6502_1_Async/cpu.v +define+SIM

sccom -reportprogress -g -work work ../sc_mem.cpp -DDEBUG_MESSAGE_REGISTER

sccom -reportprogress -g -work work ../sc_CPU6502.cpp -DCOSIM_VERILOG

sccom -reportprogress -g -work work ../Apple2.cpp -DCOSIM_VERILOG

sccom -link -lcomdlg32

설명이 필요 없을만큼 단순하다. 합성하기 전의 소스 컴파일에는 별다른 옵션이 필요없다. 옵션이 많이 들어간다면 뭔가 조치가 필요할 만큼 문제가 있다는 뜻이 아닐까?

3. 시뮬레이션 스크립트

컴파일을 마쳤으면 실행 시킬 차례다. 소프트웨어의 실행 파일 .exe는 저장장치에 놓여 있다가 사용자의 명령(GUI 운영체제에서는 실행파일을 더블클릭)에 따라 목표 운영체제에서 메모리에 적재된 후 작동한다. 하드웨어 언어의 문장은 병렬실행(concurrent execution)이다. 따라서 일반적인 소프트웨어 운영체제에서 실행 될 수 없다. QuestaSim의 병렬 시뮬레이션 커널에서 실행 시켜야 한다. 실행 명령은 vsim 이다.

Project_6502 예제의 스크립트는 TB/MTI 폴더에 있다. 그중 한 시뮬레이션 스크립트를 보면 다음과 같다.

# Vendor: GoodKook

# Associated Filename: simulate.do

# Purpose: SystemC testbench

# Revision History: 24 Jul 2023

#*********************************************

역시 간단하다. work 폴더에 있는 컴파일 된 모듈 중 sc_main을 최상위 모듈로 삼아 시뮬레이션을 진행하도록 적재(load) 하라는 명령 뿐이다.

입출력 신호들의 파형을 보고 싶다면 시뮬레이션을 실시하기 전에 파형(waveform) 창에 추가 시켜주자.

add wave sim:/sc_main/u_sc_CPU6502_Top/u_sc_CPU6502/reset

add wave sim:/sc_main/u_sc_CPU6502_Top/u_sc_CPU6502/AB

add wave sim:/sc_main/u_sc_CPU6502_Top/u_sc_CPU6502/DI

add wave sim:/sc_main/u_sc_CPU6502_Top/u_sc_CPU6502/DO

add wave sim:/sc_main/u_sc_CPU6502_Top/u_sc_CPU6502/WE

add wave sim:/sc_main/u_sc_CPU6502_Top/u_sc_CPU6502/IRQ

add wave sim:/sc_main/u_sc_CPU6502_Top/u_sc_CPU6502/NMI

add wave sim:/sc_main/u_sc_CPU6502_Top/u_sc_CPU6502/RDY

4. 실행

QuestaSim을 실행 시켜 작업 폴더로 이동 후 컴파일 스크립트 실행

컴파일이 무사히 완료되면 work 라이브러리들이 표시된다. Verilog 모듈과 SystemC 모듈이 보인다.

시뮬레이션 스크립트를 실행하여 최상위 모듈을 적재한다. 최상위 모듈 sc_main 아래로 SystemC 로 작성된 메모리 모델 sc_mem과 Verilog RTL 모델이 계층적으로 구성되었음을 알 수 있다.

QuestaSim에 적재된 시뮬레이션 모듈들은 CPU와 메모리 뿐이다. 6502 CPU의 입출력 장치는 윈도우즈의 키보드와 화면을 통해 구동하기로 한다.

MSVC의 "Apple2_Screen" 을 먼저 실행 시켜 놓은 후 QuestaSim의 커맨드 창에 실행 명령을 준다. 실행 명령은 run 이다.

QuestaSim에서 실행되는 Verilog의 CPU와 윈도우즈에서 구현된 입출력장치 어플리케이션 'Apple ][ screen'을 구동하는 모습을 보여준다. 이것이 Co-Simulation 이다.

-----------------------------------------------------------------------------

예제 실습: "Verilog RTL에서 GDS 레이아웃 까지"

[이전] Project_6502 예제의 SystemC 테스트 환경 빌드 및 실행하기

[다음] Project_6502 예제의 합성 후 Co-Simulation 실시 방법

Project_6502 예제의 SystemC 테스트 환경 빌드 및 실행하기

예제 실습: "Verilog RTL에서 GDS 레이아웃 까지"[2/4]

Project_6502 예제의 SystemC 테스트 환경 빌드 및 실행하기

Verilog HDL과 SystemC 테스트 벤치의 Co-Simulation 예제 중 SystemC/C++ 테스트 환경을 빌드하고 실행 하는 방법을 설명한다.

목차:

1. 사전 준비

예제를 수행하기 위해 다음과 같은 시뮬레이션 도구와 사전 라이브러리가 구축되어야 한다.

사전준비는 아래의 링크에 따라 설치한다.

https://fun-teaching-goodkook.blogspot.com/2023/08/systemc-sdl2.html

2. 예제 내려받기

아래 링크에서 예제를 내려받아 압축을 푼다.

https://drive.google.com/file/d/152hO9EkAhfQ6mv0biaNVylZcI79n-4Sa/view?usp=drive_link

압축을 푼 후 폴더 구조에 유의하자.

3. SystemC 테스트 환경 "Apple2" 빌드

예제를 푼 폴더에서 MSVC 폴더를 찾아 들어가면 Apple2.sln 이 있다.

이 프로젝트를 더블-클릭하여 VisualStudio 를 실행시킨다. "Apple2"를 빌드 해보자.

헤더 파일 systemc.h 를 찾을 수 없다는 메시지.

SystemC 는 MSVC C++의 기본 라이브러리가 아니기 때문이다. 앞서 구축한 SystemC 의 소스 폴더를 인클루드 검색 폴더에 추가 시켜야 한다.

컴파일 옵션을 확인하자. 헤더파일 systemc.h 는 앞서 systemc-2.3.3의 압축을 풀었던 폴더안에 있다.

프로젝트 옵션 중 Additional Include Directories 에 추가 시키자.

그외 SystemC 라이브러리를 구축할 때 사용했던 옵션들과 일치하는지 확인해 두자.

그리고 드러나지 않은 옵션이 하나 더있다. MSVC++가 표준 C++를 완벽히 지원하지 않아서 생긴 것이라고 한다. 사실 표준으로 제정된 C++ 가 워낙 방대해서 이를 모두 준수하는 컴파일러는 없다고 한다.

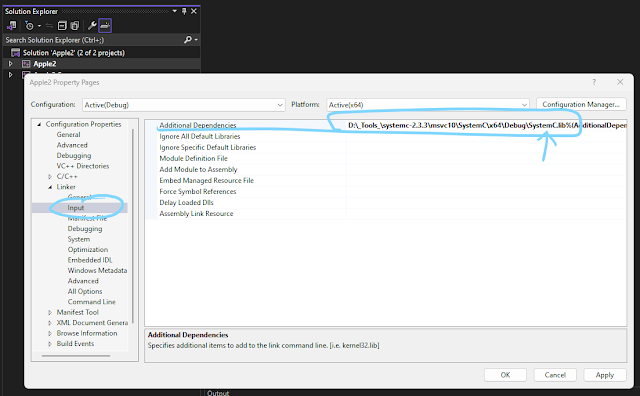

다시 "Apple2"를 빌드하면 컴파일은 순조롭게 진행 되지만 링크(Link)에서 수많은 오류가 난다. 대부분 un-resolved external 들이다. 우리가 사용하려는 SystemC 가 기본 라이브러리가 아니었기에 앞서 만들어 두었던 SystemC.lib를 추가 시켜야 한다.

앞서 구축한 SystemC.lib가 저장된 곳을 찾아보자.

이 라이브러리 파일을 프로젝트의 링커 옵션에 추가 시킨다.

4. 입출력 드라이버 "Apple2_Screen" 빌드

앞서 컴파일한 "Apple2"는 6502 CPU의 HDL을 검증하기 위한 Co-Simulation 테스트 벤치였다. "Apple2_Screen"은 6502 CPU를 채택한 컴퓨터를 구성하려고 한다. 기본 입출력 장치로 화면과 키보드를 SDL2 라이브러리를 활용하여 컴파일 한다.

예제의 ...\Project_6502\Apple2_Co-Sim\TB\MSVC\Apple2_Screen 에 MSVC 프로젝트 파일이 있다. 더블 클릭하여 빌드하면 헤더파일 SDL.h을 찾지 못한다는 오류 메시지를 보게된다. SDL2 의 압축을 풀었던 폴더에서 include 에 SDL.h 가 있다. 컴파일러 Additional Include Directories 에 추가시키자. 이 프로젝트는 SystemC 를 사용하지 않으므로 다른 옵션을 수정할 필요는 없다.

링크 시 un-resolved externals 라는 에러가 나올텐데 이 역시 SDL2.lib 를 추가시키지 않았기 때문이다. 찾아서 Linker:Input의 Additional dependencies 에 추가시키자.

다시 빌드하면 무난히 컴파일이 끝난다.

5. 실행

아직 Verilog 를 포함하지 않은 단계이지만 SystemC 만으로 만들어 놓은 테스트 환경만 실행시켜보자. 두개의 MSVC 어플리케이션을 만들어 놓았다. 두 어플리케이션 사에에 통신은 Windows IPC 중 PIPE 를 통해 데이터를 주고 받는다.

Apple2 테스트 벤치는 여러가지 시험을 할 수 있도록 작성되었다. sc_CPU6502.h 에 어떤 테스트를 할지 결정하는 define 매크로가 있다.

매트로 정의 #define 앞에 붙은 코멘트를 제거함으로써 테스트할 항목을 지정할 수 있다. 키보드 입출력을 테스트 하려면 아래와 같이 코멘트를 지우고 Re-Build 한다.

#define TEST_KEYBOARD

"Apple2_Screen" 프로젝트를 활성화 한 후 F5 키를 눌러 실행 시킨다. 이어 "Apple2" 프로젝트에서 F5를 눌러 실행 시행킨다. MSVC에서 F5 키는 디버그 실행을 의미한다. 그외, F9는 브레이크 설정, F10, F11은 소스코드 trace-in/out이다. MSVC의 다양한 디버깅 기법을 스스로 익혀보기 바란다.

"Apple2_Screen" 을 실행시켜 화면에 띄워진 "Apple ][ screen" 에 타이핑을 하면 입출력되는 모습을 보게 될 것이다.

* Verilog로 작성된 RTL의 CPU가 사용할 메모리를 SystemC 로 모델링 하였다. 이 메모리 모델이 추후 적용할 CPU에서 읽기 및 쓰기 동작에 부합 하는지 테스트 하기 위해 sc_CPU6502 라는 SystemC 모듈이 작성 되었다. 이 모듈은 실제로 6502 CPU의 기능을 수행 하지 않고 단지 메모리 접근 타이밍 만을 모델링 한 것이다. 이런 모델을 BFM (Bus Functional Model) 이라 한다.

6. 요망사항

아직 Co-Simulation 단계에 들어가지 않았고 SystemC/C++ 로 Verilog HDL을 검증하기 위한 환경을 구축하였다. 예제의 C++와 SystemC를 모두 이해하려면 다소 시간이 필요하다. 앞으로 수차례에 걸쳐 살펴볼 것이다. 너무 어렵게 생각하지 않길 바라며 현재 위치에서 소스를 훑어보고 전체적인 구조와 흐름을 파악해 보자. 추후 강의 시간에 질문할 꺼리가 생기길 바란다.

2023년 8월 16일 수요일

SystemC 및 SDL2 라이브러리 빌드 하는 방법

예제 실습: "Verilog RTL에서 GDS 레이아웃 까지"[1/4]

SystemC 및 SDL2 라이브러리 빌드 하는 방법

반도체 설계 HDL을 검증하기 위한 도구로서 SystemC와 SDL2을 적극 활용한다. 이에 필요한 라이브러리를 구축하는 방법을 설명한다.

목차:

A. 선행 설치할 컴파일러 도구들

1. VisualStudio 2022 Community Edition

- VisualStudion Installer에서 [수정] 버튼을 눌러 다음과 같이 설치되었는지 확인

C++ 를 이용하여 윈도우즈용 어플리케이션을 빌드하기 위한 도구 필수 선택

"C++를 사용한 데스크톱 개발" 항목에서 "설치세부정보">"선택사항" 중, 'MSVC v143 빌드도구 C++ MFC', 'Windows 11 SDK' 항목이 포함되었는지 확인 후 설치 포함 시킬것

추가 사항으로 "VisualStudio 확장개발", "C++를 사용한 Linux 및 임베디드 개발"

2. QuestaSim/ModelSim Intel FPGA Starter Edition

인텔 FPGA 개발도구 Quartus 에 포함되어 있으나 독립 설치 할 수 있음. 설치 방법은 아래 링크 참조

https://fun-teaching-goodkook.blogspot.com/2023/07/questasimmodelsim.html

B. 선행 구성이 필요한 라이브러리

1. SystemC

https://www.accellera.org/images/downloads/standards/systemc/systemc-2.3.3.tar.gz

압축을 푼 폴더 탐색하여 MSVC 프로젝트(솔루션) 파일 더블클릭

......\systemc-2.3.3\msvc10\SystemC\SystemC.sln

VisualStudio 'Solution Explorer'의 SystemC의 빌드 옵션 변경

* Multi-Threaded Debug DLL 로 해도 좋으나 추후 어플리케이션 exe를 빌드할 때 맞춰 줄 것. 타 컴퓨터에서 어플리케이션 실행을 위해 VisualStudio C++ 런타임 DLL을 설치하는 절차가 필요함. 그외 디버깅 할 때 DLL을 로딩하는 경우가 생겨서 불편함.

C++:Language의 Enable Run-Time Type Information 에 Yes(/GR) 선택

컴파일 옵션 설정을 완료하고 SystemC 라이브러리 Build 하면 x64\Debug 에 SystemC.lib 가 생성 되었으므로 확인 할 것

2. SDL2

Simple Direct Layer 사이트를 방문하여 최신 소스코드를 내려받기

https://www.libsdl.org/

* SDL은 2D 게임 제작용으로 널리 사용되는 라이브러리인데 각종 멀티미디어 설계의 테스트벤치 제작용에 유용하게 사용할 수 있음. 익혀두면 널리 이로울 것임

압축을 푼 후 VisualC 폴더에 SDL.sln 실행하면,

프로젝트 하위 폴더에 SDL2.dll과 SDL2.lib 파일이 생성되어 있음

-----------------------------------------------------------------

예제 실습: "Verilog RTL에서 GDS 레이아웃 까지"

[다음] Project_6502 예제의 SystemC 테스트 환경 빌드 및 실행하기

2023년 8월 15일 화요일

[주간 세미나/강좌 공지] 오픈 소스 표준 셀 기반 설계(2) (2023년 8월 16일)

[주간 세미나/강좌 공지] 오픈 소스 표준 셀 기반 설계(2) (2023년 8월 16일)

내용:

[주간 세미나]

2023년 8월 14일 월요일

OpenRAM 오픈소스 메모리 컴파일러(RAM/ROM 생성기)

OpenRAM 오픈소스 메모리 컴파일러(RAM/ROM 생성기)

시스템 반도체에서 소프트웨어는 큰 비중을 차지한다. CPU 뿐만 아니라 기본 펌웨어(모니터)를 운영하기 위해 메모리를 내장 토록한다. 메모리는 치밀하게 반복된 구조를 가지고 있을 뿐만 아니라 디지털 비트로 따지면 매우 규모가 크다. 따라서 집적도가 높도록 따로 모아 생성한다.

OpenRAM은 메모리 RAM과 ROM을 생성해주는 도구다. 아래 링크를 참조한다.

설치는 Git 을 통해 생성 스크립트를 내려 받을 수 있다. 주로 Python과 Makefile을 이용한 스크립트들이고 그외 PDK 가 필요하다. 도커(docker) 기반으로 설치하는 까닭에 온갖 것들을 다 끌어와서 쓸데없이 용량이 커진다(Python 기반이라 anaconda 또는 miniconda와 관련 패키지를 모두 끌어온다). 나중에 설치 최적화 할 때 정리하면 좋겠으나 설명 문서에 따르면 폴더구조를 바꾸지 말기를 권장 하고 있다.

스크립트를 내려받자.

$ git clone https://github.com/VLSIDA/OpenRAM

준비된 예제를 실행 시켜보자.

파라메터 없이 make 유틸리티를 실행하면 아래와 같은 메시가 나타난다. 준비된 예제들의 목록이다.

(which is version v1.2.29)

SRAM Configurations:

- example_config_1rw_1r_scn4m_subm

- example_config_1rw_1w_scn4m_subm

- example_config_1rw_2mux_scn4m_subm

- example_config_1w_1r_scn4m_subm

- example_config_2rw_scn4m_subm

- example_config_big_scn4m_subm

- example_config_freepdk45

- example_config_giant_scn4m_subm

- example_config_medium_scn4m_subm

- example_config_scn4m_subm

- freepdk45_sram_1rw1r_32x2048_8

- scn4m_subm_sram_16kbyte_1rw1r_32x4096_8

- scn4m_subm_sram_1kbyte_1rw1r_32x256_8

- scn4m_subm_sram_2kbyte_1rw1r_32x512_8

- scn4m_subm_sram_32kbyte_1rw1r_2x32x4096_8

- scn4m_subm_sram_4kbyte_1rw1r_32x1024_8

- scn4m_subm_sram_8kbyte_1rw1r_32x2048_8

- sky130_sram_1kbyte_1r1w_8x1024_8

- sky130_sram_1kbyte_1rw1r_32x256_8

- sky130_sram_1kbyte_1rw1r_8x1024_8

- sky130_sram_1kbyte_1rw_32x256_8

- sky130_sram_1rw1r_tiny

- sky130_sram_1rw_tiny

- sky130_sram_2kbyte_1rw1r_32x512_8

- sky130_sram_2kbyte_1rw_32x512_8

- sky130_sram_4kbyte_1rw1r_32x1024_8

- sky130_sram_4kbyte_1rw_32x1024_8

- sky130_sram_4kbyte_1rw_64x512_8

ROM Configurations:

- sky130_rom_1kbyte

이 중에서 하나를 골라서,

메모리 컴파일러를 작동 시키기 위한 도구들을 검사하는데, 처음 실행인 경우 OpenRAM/miniconda 에 독립 실행할 수 있도록 도커(docker)를 구성한다. 이때 온갖 필요한 패키지들을 끌어온다. OpenRAM/miniconda/bin 폴더를 보면 익히 봐왔던 magic, netgen 등이 포함되어 있음을 알 수 있다. 굳이 이래야 하나 싶지만 하드디스크 용량은 풍부하고 사용자 마다 설치 환경이 다르니 일일이 설치하는데 곤란을 겪지 않도록 배려 했다. 도커(Docker)의 큰 목적 이기도 하고......

도커를 구성하던 중간에 에러 메시지가 뜬다.

ERROR: Could not open requirements file: [Errno 2] No such file or directory: 'requirements.txt'

도커를 구성하는데 필요한 패키지 목록 파일을 못찾았다는 불평이다. 이어서, 아래와 같은 문구를 보게 된다.

File "/home/goodkook/opencircuits/OpenRAM/sram_compiler.py", line 42, in <module>

openram.init_openram(config_file=args[0])

File "/home/goodkook/opencircuits/OpenRAM/compiler/globals.py", line 205, in init_openram

from openram import characterizer

File "/home/goodkook/opencircuits/OpenRAM/compiler/characterizer/__init__.py", line 14, in <module>

from .linear_regression import *

File "/home/goodkook/opencircuits/OpenRAM/compiler/characterizer/linear_regression.py", line 8, in <module>

from sklearn.linear_model import Ridge

ModuleNotFoundError: No module named 'sklearn'

make[1]: *** [Makefile:85: example_config_1rw_1w_scn4m_subm.ok] Error 1

make: *** [Makefile:95: example_config_1rw_1w_scn4m_subm] Error 2

Make 유틸리티가 작동 하면서 에러가 났을 경우 그 이유를 보려준다. Python의 sklearn 이라는 모듈이 설치되어 있지 않다고 한다. Python의 추가 모듈 설치는 pip로 한다.

$ sudo pip3 install scikit-learn

다시 make 유틸리티를 실행 시켜보자.

$ make example_config_1rw_1r_scn4m_subm

필요한 도구들이 준비되었다면 성공적으로 메모리가 생성될 것이다. 이제 도구는 준비되었다. PDK에 맞도록 포팅할 일이 남았다.