"Verilog-Verilator-SystemC 방법론 기초"

[부록] FIR 필터 PE 의 "내 칩MPW" 제출용 GDS 생성

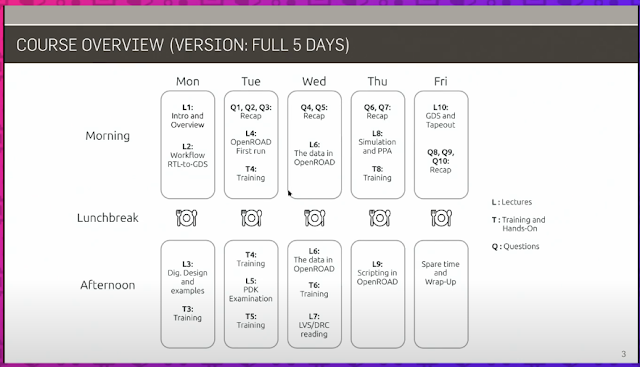

"Verilog-Verilator-SystemC 방법론 기초"는 "내 칩(My Chip) MPW 서비스": 오픈-소스 도구 활용 반도체 설계 특별과정 중 두번째 강좌로서 베릴로그(Verilog)와 오픈-소스 시뮬레이션 도구 Verilator 그리고 시스템 수준 검증 방법론 SystemC의 입문 과정이다. 컴퓨팅 언어를 활용한 디지털 회로의 설계와 검증을 다룬다(Quantative approach to digital circuit design using computing language and Open-Source EDA tools).

강의 내용은 아래와 같다.

[1] 도구 설치 [링크]

[2] 설계 언어 Verilog 와 검증 언어 SystemC/C++[링크]

[3] 하드웨어 기술 언어의 코딩 스타일[링크]

[4] 실습: 쉬프트 레지스터 [링크]

[5] 실습: FIR 필터 [링크]

[6] "내 칩 MPW" 요건에 맞춘 FIR 필터의 PE 설계[링크]

[부록] FIR 필터 PE의 "내 칩MPW" 제출용 GDS 생성[링크]

----------------------------------------------------------

목차

i. 사전준비

i-1. 디자인 킷(Design Kit) 내려받기

i-2. 디렉토리 구조/심볼 링크 걸기

i-3. 오픈- 소스 도구 설치(Installing Open-Source Tools)

ii. PE 합성, 자동 배치 및 배선, 레이아웃 검사(Synthesis, Auto-P&R, Layout Check)

ii-1. 합성(Synthesize)

ii-2. 합성 후 시뮬레이션(Post-Synthesis/Netlist Timing Simulation)

ii-3. 자동 배치(Auto-Placement)

ii-4. 자동배선(Auto-Routing)

ii-5. 표준 셀 병합 레이아웃 생성(Migration)

ii-6. LVS 검증

ii-7. DRC: 디자인 룰 검사

iii. 적층 비아 검사(Stacked VIA Check)

iv. 레이아웃 네트리스트 시뮬레이션(Layout Netlist Switch-Level Simulation)

v. 입출력 패드 부착(IO Pad)

v-1. 최상위 레이아웃 작업 디렉토리, chip_top

v-2. 칩 마킹/로고(Chip Marking/Logo)

v-3. 패드 배치 계획(Chip-Top plan)

v-4. 패드 배치 및 배선(Edit Chip-Top & Pad routing)

vi. 최종 GDS 생성(Final GDS generation)

vii. GDS 복기 (Review GDS)

-----------------------------------------------------------

i. 사전 준비

"내 칩MPW" 제출용 GDS 생성에 사용된 오픈-소스 반도체 설계 자동화 도구들은 다음과 같다.

- Yosys, RTL synthesizer, https://github.com/YosysHQ

- GrayWolf, Auto-Placer, https://github.com/rubund/graywolf

- QRouter, Auto-Router, https://github.com/RTimothyEdwards/qrouter

- Magic, VLSI layout editor, https://github.com/RTimothyEdwards/magic

- KLayout, layout tool, https://www.klayout.de/

- Netgen, LVS & LVL Netlist compare, https://github.com/RTimothyEdwards/netgen

- QFlow with ETRI050 tech., https://github.com/RTimothyEdwards/qflow

- SystemC, C++ class library for system level simulation & modeling, https://systemc.org/

- Verilator, Verilog to SystemC/C++ converter, https://www.veripool.org/verilator/

- gtkWave, digital waveform viewer, https://gtkwave.sourceforge.net/

- ICARUS Verilog, HDL Simulator, https://github.com/steveicarus/iverilog

i-1. 디자인 킷 내려받기

표준 셀 기반 RTL 디자인 킷(Standard Cell Based RTL Design Kit)과 각 도구의 설치 스크립트는 아래의 깃-허브 저장소(github repository)에서 내려받을 수 있다.

https://github.com/GoodKook/ETRI-0.5um-CMOS-MPW-Std-Cell-DK.git

설계를 수행할 컴퓨팅 환경(운영체제)는 마이크로소프트 윈도우즈 11의 WSL2(Windows Sub-system Linux)에 설치된 리눅스 우분투 20.04 LTS 다. WSL2와 우분투의 설치 방법은 아래 링크를 참조한다.

리눅스 및 VLSI 레이아웃 오픈-소스 도구 설치[링크]

리눅스 터미널을 열어 리눅스 프롬프트에서 git 명령으로 경희대학교 디자인-킷을 내려 받는다.

$ cd

$ git clone https://github.com/GoodKook/ETRI-0.5um-CMOS-MPW-Std-Cell-DK.git

이 디자인 킷의 튜토리얼 디렉토리에 "내 칩(My Chip) MPW 서비스": 오픈-소스 도구 활용 반도체 설계 특별과정 예제들이 모두 포함되어 있다.

i-2. 디렉토리 구조: 심볼 링크 걸기

내려받은 디자인 킷의 디렉토리 이름이 매우 길어 번거롭다. 아래와 같이 심볼링크를 걸어두자.

$ ln -s ~/ETRI-0.5um-CMOS-MPW-Std-Cell-DK ETRI050_DesignKit

디자인 킷의 폴더 구조는 아래와 같다.

표준 셀라이브러리가 저장된 디렉토리 digital_ETRI050_m2d 를 digital_ETRI로 심볼 링크를 건다.

$ cd ~/ETRI050_DesignKit/

$ ln -s digital_ETRI050_m2d digital_ETRI

앞으로 진행할 실습의 예제의 디렉토리는 ~/ETRI050_DesignKit/Tutorials/2-6_Lab4_FIR_PE 다. 설계 과정마다 사용할 하위 디렉토리를 두고 있다. 예제를 다른 디렉토리로 옮겼을 경우 경로명에 유의한다.

베릴로그 RTL에서 반도체 제조 공정용 GDS를 얻기까지 여러 단계의 추상화 낮춤 과정(Lowering Abstraction Level)을 거친다. 그 과정의 각 단계마다 수많은 중간 파일들이 생성된다. 이 파일들의 역활과 용도의 이해는 매우 중요하다. 중간 파일이 삭제되거나 변경될 경우 모든 수고가 수포로 돌아가는 불상사가 생긴다. 이런 실수는 인간에 의해 발생 되기도 하지만 자동화 도구에 의해 저질러 질 수도 있다. 자동화 도구에 의해 생성되는 파일의 이름이 겹치는 경우 중요 설계 파일을 잃게 된다. 설계 과정 중 추상화 단계 마다 디렉토리로 관리하는 방법은 기초적이지만 사고 예방에 효과적이다.

i-3. 오픈- 소스 도구 설치

디자인 킷을 내려받게 되면 쉘 스크립트 들이 일반 텍스트 파일로 저장된다. 모두 실행가능한 쉘 스크립트, 파이썬 스크립트가 되도록 실행 속성을 부여해준다.

$ cd

$ chmod +x ~/ETRI050_DesignKit/Tools/*.sh

$ chmod +x ~/ETRI050_DesignKit/scripts/*.sh

$ chmod +x ~/ETRI050_DesignKit/scripts/*.py

Tools 디렉토리에 반도체 설계 오픈-소스 도구들을 모두 설치할 수 있는 스크립트 build_tools.sh 가 있다.

$ cd ~/ETRI050_DesignKit/Tools

$ ./build_tools.sh이 스크립트로 설치할 도구들은 아래와 같다.

gsl: GNU Scientific Library

graywolf: GrayWolf Auto Placer

qrouter: Auto-Router

irsim: IRSim Switching Level Simulator

magic: VLSI Layout Tool

klayout: Layout Tool

netgen: NetGen Layout vs Schematic compare

ngspice43: SPICE simulator

xschem: XSchem Schematic entry tool

SystemC: SystemC

iverilog: iVerilog HDL simulator

Verilator: Verilog to C++/SystemC converter

gtkwave: gtkWave Digital waveform viewer

yosys: Yosys RTL Synthesizer

QFlow: qflow-1.4.100_etri050

인터넷을 통해 각 도구들의 원시 코드들을 내려 받고 빌드한다. 설치할 도구들이 상당히 많아서 완료하기까지 한시간 이상 소요된다. 중간에 설치를 위해 관리자 비밀번호(password)를 입력해야 하므로 컴퓨터 앞을 떠나지 않도록 한다. 개별 도구의 설치 스크립트도 있으므로 활용토록 한다.

ii. PE 합성 및 자동 배치 배선(Synthesis and Auto-P&R)

예제 디렉토리에 합성과 자동 배치배선을 수행할 수 있는 Makefile 이 준비 되어 있다. 각 도구들의 사용법은 추후 강좌에서 자세히 다룬다.

ii-1. 합성(Synthesize)

베릴로그 RTL의 합성기는 Yosys다.

$ cd ~/ETRI050_DesignKit/2-6_Lab4_FIR_PE

$ make synthesize

합성 로그를 통해 베릴로그 RTL 을 읽어 합성하는 과정을 볼 수 있다. 합성 로그 파일은 log/synth.log다. 그 일부는 아래와 같다.

디자인 킷의 리버티(Liberty) 파일 etri05_stdcells.lib 에서 표준 셀의 목록을 먼저 읽는다. 이어 설계 베릴로그 구문으로부터 논리식과 플립플롭, 래치 들을 추출 한다.

qflow synthesize -T etri050 fir_pe

--------------------------------

Qflow project setup

--------------------------------

Technology set to etri050

Regenerating files for existing project fir_pe

Running yosys for verilog parsing and synthesis

yosys -s fir_pe.ys

/----------------------------------------------------------------------------\

| yosys -- Yosys Open SYnthesis Suite |

| Copyright (C) 2012 - 2024 Claire Xenia Wolf <claire@yosyshq.com> |

| Distributed under an ISC-like license, type "license" to see terms |

\----------------------------------------------------------------------------/

Yosys 0.44+39 (git sha1 27c143225, clang++ 10.0.0-4ubuntu1 -fPIC -O3)

-- Executing script file `fir_pe.ys' --

1. Executing Liberty frontend:

/usr/local/share/qflow/tech/etri050/etri05_stdcells.lib

Imported 39 cell types from liberty file.

2. Executing Verilog-2005 frontend:

/home/goodkook/ETRI050_DesignKit/Tutorials/2-6_Lab4_FIR_PE/source/fir_pe.v

Parsing Verilog input from `/home/goodkook/ETRI050_DesignKit/Tutorials/2-6_Lab4_FIR_PE/source/fir_pe.v' to AST representation.

Generating RTLIL representation for module `\fir_pe'.

Successfully finished Verilog frontend.

베릴로그 RTL로부터 추출한 논리식을 최적화 도구 ABC를 사용하여 최적화 한다.

3. Executing SYNTH pass.

.......

3.22. Executing ABC pass (technology mapping using ABC).

3.22.1. Extracting gate netlist of module `\fir_pe' to `<abc-temp-dir>/input.blif'..

Extracted 365 gates and 429 wires to a netlist network with 64 inputs and 41 outputs.

3.22.1.1. Executing ABC.

Running ABC command: "<yosys-exe-dir>/yosys-abc" -s -f <abc-temp-dir>/abc.script 2>&1

ABC: ABC command line: "source <abc-temp-dir>/abc.script".

ABC:

ABC: + read_blif <abc-temp-dir>/input.blif

ABC: + read_library <abc-temp-dir>/stdcells.genlib

ABC: Entered genlib library with 13 gates from file "<abc-temp-dir>/stdcells.genlib".

ABC: + strash

ABC: + dretime

ABC: + map

ABC: + write_blif <abc-temp-dir>/output.blif

3.22.1.2. Re-integrating ABC results.

ABC RESULTS: MUX cells: 16

ABC RESULTS: NOT cells: 6

ABC RESULTS: AND cells: 37

ABC RESULTS: XNOR cells: 30

ABC RESULTS: OR cells: 36

ABC RESULTS: NAND cells: 33

ABC RESULTS: ORNOT cells: 12

ABC RESULTS: NOR cells: 30

ABC RESULTS: ANDNOT cells: 93

ABC RESULTS: XOR cells: 76

ABC RESULTS: internal signals: 324

ABC RESULTS: input signals: 64

ABC RESULTS: output signals: 41

............

디자인 킷에서 제공하는 표준 셀로 매핑하여 최종 네트리스트를 얻는다. 베릴로그 네트리스트 fir_pe.rtlnopwr.v 는 P&R에, SPICE 네트리스트 fir_pe.spc 는 LVS의 목적으로 사용된다.

12. Printing statistics.

=== fir_pe ===

Number of wires: 741

Number of wire bits: 833

Number of public wires: 741

Number of public wire bits: 833

Number of ports: 8

Number of port bits: 25

Number of memories: 0

Number of memory bits: 0

Number of processes: 0

Number of cells: 813

AND2X2 30

AOI21X1 72

AOI22X1 17

BUFX2 9

DFFPOSX1 75

INVX1 111

NAND2X1 147

NAND3X1 83

NOR2X1 62

OAI21X1 173

OAI22X1 7

OR2X2 8

XNOR2X1 7

XOR2X1 12

Running vlog2Verilog for antenna cell mapping.

vlog2Verilog -c -p -v vdd -g gnd -l ...../etri050_stdcells.lef

-o fir_pe.v fir_pe_sized.v

Generating RTL verilog and SPICE netlist file in directory

~/ETRI050_DesignKit/Tutorials/2-6_Lab4_FIR_PE/synthesis

Files:

Verilog: synthesis/fir_pe.rtl.v

Verilog: synthesis/fir_pe.rtlnopwr.v

Verilog: synthesis/fir_pe.rtlbb.v

Spice: synthesis/fir_pe.spc

......

Synthesis script ended on Fri 23 Aug 2024 01:48:17 PM KST

ii-2. 합성 후 기능 검증(Post Synthesis Simulation)

합성을 거치면서 RTL 에서 표준 셀의 네트리스트로 추상화 수준이 낮춰졌다. 표준 셀은 디지털 논리소자들(게이트와 플립플롭)을 뜻한다. 클럭의 시간순 행위 묘사에서 논리회로로 변경된 셈이다. 자동화 도구 합성기(synthesizer)에 의해 수행되는 매우 급격한 추상성 변화다. 기능성의 등가를 시뮬레이션을 통해 확인 한다.

디지털 논리소자의 모델에 시간 지연 정보를 담고 있으므로 합성으로 얻은 소자들의 경로를 바탕으로 타이밍 시뮬레이션도 가능하다. 다만 오픈-소스 Verilator 도구의 한계로 인해 표준셀의 시간 모형 베릴로그를 완벽히 지원하지 못한다. 베릴로그 모형을 가지고 논리 회로의 기능수준에서 검증을 실시한다.

표준 셀의 기능 수준 베릴로그 모형과 타이밍 모형을 비교하면 아래와 같다.

HDL 전용 시뮬레이터를 사용하면 타이밍 시뮬레이션이 가능하다. 표준 셀의 타이밍 베릴로그 모델과 기능 모델은 디자인 킷의 표준 셀 디렉토리에 있다. 타이밍 모델은 khu_etri05_stdcells.v 이다. 기능 모델 khu_etri05_stdcells_func.v 이다.

Verilator로 합성 후 베릴로그 네트리스트 시뮬레이션의 실행은 다음과 같다. 테스트 벤치는 RTL 시뮬레이션 때와 동일한 SystemC 환경이다. Verilator로 변환 한 fir_pe의 베릴로그 네트리스트 synthesis/fir_pe.v 와 지연정보없는 표준 셀 베릴로그 라이브러리를 digital_ETRI/khu_etri05_stdcells_func.v를 시뮬레이션 모델로 쓴다.

$ make clean

$ make build_net

$ make run

Verilator는 UDP를 사용하는 타이밍 모델을 변환 할 수 없다. 타이밍 시뮬레이션을 위해 오픈-소스 베릴로그 시뮬레이터 iVerilog 를 사용한다.

$ iverilog -g2005-sv -gspecify -o fir_pe \

~/ETRI050_DesignKit/digital_ETRI/khu_etri05_stdcells.v \

../synthesis/fir_pe.v fir_pe_TB.v

준비된 메이크 스크립트를 사용하면,

$ make clean

$ make build_tim

$ make run_tim

베릴로그 테스트 벤치로 수많은 테스트 벡터를 동적으로 생성하기는 거의 불가능하다. 베릴로그는 프로그래밍 언어로 작성된 함수를 연결 할 수 있는 VPI(Verilog Procedural Interface)표준을 가지고 있다. iVerolog는 SystemVerilog의 DPI 표준을 아직 지원하지 않고 있다.

VPI 를 통해 SystemC 테스트 벤치를 활용할 수 있다. Verilator로 변환한 모델 source/fir_pe.v 와 SystemC 테스트벤치 그리고 VPI를 통해 베릴로그 DUT와 테스트 벤치를 모두 통합한 검증 환경은 아래와 같다. 합성한 네트리스트와 표준 셀 타이밍 모델을 DUT로 사용하여 시뮬레이션 할 수 있다.

예제에 VPI와 SystemC 테스트 벤치 활용 타이밍 시뮬레이션용 메이크 스크립트를 포함해 두었다.

$ cd ~/ETRI050_DesignKit/Tutorials/2-6_Lab4_FIR_PE/simulation

$ cd sc_vpi_co-sim

$ make build_tim

$ make run

$ make wave

VCD 파형으로 지연을 관찰 할 수 있다.

ii-3. 자동 배치(Auto-Placement)

자동배치를 실시하기 전에 핀 배치 파일 fir_pe.cel2 을 만들어 두자.

$ cd ~/ETRI050_DesignKit/2-6_Lab4_FIR_PE

$ touch layout/fir_pe.cel2

이어서 자동 배치 수행,

$ make place

자동배치의 로그 파일은 log/place.log 다. 로그 파일을 살펴보자. 먼저 LEF(Library Exchange Format) 파일에서 배치에 사용할 표준 셀의 크기와 입출력 포트 정보를 읽는다.

qflow place -T etri050 fir_pe

--------------------------------

Qflow project setup

--------------------------------

Technology set to etri050

Regenerating files for existing project fir_pe

Qrouter detail maze router version 1.4.87.T

Reading LEF data from file

/usr/local/share/qflow/tech/etri050/etri050_stdcells.lef.

......

LEF Read: encountered 0 errors and 8 warnings total.

합성으로 얻은 베릴로그 네트리스트 fir_pe.rtlnopower.v 를 배치도구 graywolf 용 파일 fir-pe.cel로 변환한다.

Running vlog2Cel to generate input files for graywolf

vlog2Cel -l etri050_stdcells.lef -u 100 \

-o layout/fir_pe.cel \

synthesis/fir_pe.rtlnopwr.v

No fir_pe.cel1 file found for project. . .

no partial blockages to apply to layout.

표준 셀 배치 밀집도(initial density)와 핀 배치를 참조하여 자동 배치를 수행한다. 아래의 경우 밀집도는 0.6 다.

Running decongest to set initial density of 0.6

decongest.tcl fir_pe \

etri050_stdcells.lef FILL,,, 0.6 \

--units=100 --lib=etri05_stdcells.lib

Reading FILL {} {} {} macros from LEF file.

Unexpected input in LEF file: Only macro defs were expected!

Fixed density planning, density = 0.6

Number of cells = 847, total width = 1088100

Width of fill = 725400

Width of decap = 0

Width of antenna = 0

Width of body ties = 0

Done!

Preparing pin placement hints from fir_pe.cel2

Running GrayWolf placement

graywolf fir_pe

안테나 셀과 필러 셀 그리고 전원 선을 참조한다.

Running getantennacell to determine cell to use for antenna anchors.

getantennacell.tcl fir_pe etri050_stdcells.lef

Running getfillcell to determine cell to use for fill.

getfillcell.tcl fir_pe etri050_stdcells.lef FILL

Running place2def to translate graywolf output to DEF format.

place2def.tcl fir_pe FILL

Running addspacers to generate power stripes and align cell right edge

addspacers -stripe 8 225 PG -p vdd -g gnd -f FILL -O \

-l etri050_stdcells.lef -o fir_pe_filled.def fir_pe

Running arrangepins to adjust pin positions for optimal routing.

......

배치를 수행한 결과는 DEF(Design Exchange Format) 파일에 저장된다.

Running place2def to translate graywolf output to DEF format.

place2def.tcl fir_pe FILL

DEF database: 100 units per micron

Limits: xbot = -802.0 ybot = -795.0 xtop = 87802.0 ytop = 82395.0

Core values: 150 150 87450 82050

Offsets: 150 150

3 routing layers

278 horizontal tracks from -600.0 to 82800.0 step 300 (M1, M3, ...)

296 vertical tracks from -600.0 to 88200.0 step 300 (M2, M4, ...)

Summary: Total components = 3266

Fill cells = 2419

Other cells = 847

Done with place2def.tcl

......

배선을 수행하면서 설계의 논리식과 직접 관계는 없는 구동 버퍼 등이 추가될 수 있으므로 LVS 용 SPICE 네트리스트를 재생산한다.

Generating RTL verilog and SPICE netlist file in directory

2-6_Lab4_FIR_PE/synthesis

Files:

Verilog: synthesis/fir_pe.rtl.v

Verilog: synthesis/fir_pe.rtlnopwr.v

Verilog: synthesis/fir_pe.rtlbb.v

Spice: synthesis/fir_pe.spc

Running vlog2Spice.

vlog2Spice -i -l etri050_stdcells.sp -o fir_pe.spc fir_pe.rtl.v

ii-4. 자동배선(Auto-Routing)

자동배선 도구는 Qrouter다. 자동 배치 수행,

$ cd ~/ETRI050_DesignKit/2-6_Lab4_FIR_PE

$ make route자동배선 로그 파일은 log/route.log 다. 배선에 필요한 규칙을 얻기 위해 표준 셀 의 LEF를 읽는다. 배선에 사용할 금속 층의 종류와 두께 이격거리 그리고 배선 방향, 접점(컨택과 비아)의 크기 규칙들이 LEF에 정의 되어 있다.

--------------------------------

Qflow project setup

--------------------------------

Technology set to etri050

Regenerating files for existing project fir_pe

Running qrouter 1.4.87.T

qrouter -noc -s fir_pe.cfg

*** Running stage1 routing with defaults

Qrouter detail maze router version 1.4.87.T

Reading LEF data from file

/usr/local/share/qflow/tech/etri050/etri050_stdcells.lef.

자동배선의 결과 DEF를 읽어 배선해야 할 내용을 파악한다. 설계 명 fir_pe에 3331개의 서브 셀들이 있다. 필러 셀들이 포함되어서 합성의 결과보다 셀의 갯수가 상당히 증가했다. 배선할 네트의 수는 863개이며 고정된 네트는 없다. 배선에서 제외되는 2개의 특별 네트는 전원 VDD 과 접지 GND 다.

Reading DEF data from file fir_pe.def.

Diagnostic: Design name: "fir_pe"

Processed 0 vias total.

Processed 3331 subcell instances total.

Processed 27 pins total.

Processed 863 nets total (0 fixed).

Processed 2 special nets total (4 fixed).

DEF read: Processed 7117 lines.

Output scale = microns / 100, precision 1

There are 865 nets in this design.

*** Running stage1 routing with defaults

자동 배선에 성공했다는 메시지를 봐야한다. 만일 배선에 실패하면 표준 셀 배치 밀집도를 낮춰서 자동 배치부터 다시 진행해야 한다. 표준 셀 배치 밀집도는 project_vars.sh 에서 설정한다. 배선완료 후 DEF, fir_pe_route.def 에 저장한다. 참고로 배치만 마친 DEF 는 fir_pe_unroute.def 다.

----------------------------------------------

Progress: Stage 3 total routes completed: 7498

No failed routes!

----------------------------------------------

*** Writing DEF file fir_pe_route.def

emit_routes(): DEF file has 863 nets and 4 specialnets.

but qrouter wants to write 865 nets and specialnets.

----------------------------------------------

Final: No failed routes!

----------------------------------------------

배선으로 인해 생기는 기생 RC 값은 STA(Static Timing Analysis)에서 타이밍 분석에 활용된다. [주] 경희대학교 디자인 킷의 RC 값은 유효하지 않다.

*** Writing RC file fir_pe_route.rc

DEF2Verilog -v synthesis/fir_pe.rtlnopwr.v \

-o synthesis/fir_pe_postroute.v \

-p vdd -g gnd -l etri050_stdcells.lef fir_pe_route.def

자동 배선의 과정에서 네트리스트가 변경될 수 있다. 검증을 위해 SPICE 네트리스트를 재생성한다.

Generating RTL verilog and SPICE netlist file in directory

2-6_Lab4_FIR_PE/synthesis

Running vlog2Verilog.

vlog2Verilog -c -v vdd -g gnd -o fir_pe.rtl.anno.v \

fir_pe_postroute.v

Running vlog2Spice.

vlog2Spice -i -l etri050_stdcells.sp -o fir_pe.anno.spc \

fir_pe.rtl.anno.v

자동화 도구의 사용을 거치면서 발생할 만약의 경우를 대비하여 각 단계마다 검증용 네트리스트를 재생산하고 있다는 점에 주목하자. 이는 자동화 도구를 활용한 설계 플로우의 신뢰도를 담보하는 척도다.

ii-5. 표준 셀 병합 레이아웃 생성(Migration)

배치배선이 완료된 DEF에서 Magic 레이아웃 파일로 변환하는 과정이다. 금속층의 배선 정보를 담고 있는 DEF에 표준 셀을 병합해 넣는다.

$ cd ~/ETRI050_DesignKit/2-6_Lab4_FIR_PE

$ make migrate레이아웃 도구 Magic를 파일 변환 용도로 사용하기 위햐 그래픽 화면 없이 tcl 명령 처리기(tcl interpreter)로 실행한 후 표준 셀 LEF 와 배선한 DEF를 읽어들여 레이아웃을 생성한다.

qflow migrate -T etri050 fir_pe

--------------------------------

Qflow project setup

--------------------------------

magic -dnull -noconsole migrate_fir_pe.tcl

Starting magic under Tcl interpreter

Using the terminal as the console.

Using NULL graphics device.

Processing system .magicrc file

Input style lambda=0.30(p): scaleFactor=30, multiplier=1

Reading LEF data from file

/usr/local/share/qflow/tech/etri050/etri050_stdcells.lef.

Reading DEF data from file fir_pe.def.

DEF read, Line 13 (Error): END statement out of context.

Processed 3331 subcell instances total.

Processed 27 pins total.

Processed 863 nets total.

DEF의 좌표 단위를 Magic의 테크 파일 단위에 맞춘다.

Generating LEF output fir_pe.lef for cell fir_pe:

Diagnostic: Write LEF header for cell fir_pe

Diagnostic: Writing LEF output for cell fir_pe

Diagnostic: Scale value is 0.150000

표준 셀 레이아웃에서 내부의 포트와 트랜지스터 정보를 추출하여 회로검증용 SPICE 네트리스트를 추출 한다.

Extracting FILL into FILL.ext:

Extracting INVX1 into INVX1.ext:

Extracting NAND3X1 into NAND3X1.ext:

......

Extracting DFFPOSX1 into DFFPOSX1.ext:

Extracting CLKBUF1 into CLKBUF1.ext:

Extracting INVX8 into INVX8.ext:

Extracting fir_pe into fir_pe.ext:

exttospice finished.

레이아웃 디렉토리 layout 에 있는 Magic 의 자원 정의(resource context) 파일 .magicrc 을 참조하여 레이아웃 파일을 생성하게 되므로 표준 셀을 모아놓은 경로가 명시 되어야 한다. 테크 파일과 표준 셀의 경로(path)가 명시된 .magicrc 은 아래와 같다.

#-----------------------------------------------------

# .magicrc startup file for ETRI050 project under qflow

#-----------------------------------------------------

path sys +/usr/local/share/qflow/tech/etri050

tech load SCN3ME_SUBM.30.ETRI -noprompt

addpath ~/ETRI050_DesignKit/digital_ETRI

생성된 Magic 의 레이아웃은 ./layout/fir_pe.mag 다.

ii-6. LVS 검증

합성으로 얻은 네트리스트는 자동 배치와 배선의 과정을 거쳐 레이아웃 도면으로 변한다. 배선 자동화 도구 역시 소프트웨어로서 오류(bug)가 있을 수 있다는 점을 간과 해서는 않된다. 자동배선 도구가 엄청난 량의 네트를 배선하면서 배선이 성공적으로 수행되었다는 보고를 하더라도 안심할 수 없다. 변환이 이뤄질 때마다 등가성 검증은 필수다.

LVS(Layout Vs. Schematics)는 회로도와 레이아웃의 등가성을 확인하는 절차다. 합성과 자동배치로 얻은 네트리스트를 자동 배선 후 표준 셀 병합으로 얻은 레이아웃에서 추출한 네트리스트와 비교하여 두 트랜지스터 회로의 등가성을 확인한다. SPICE 네트리스트를 비교하는 도구는 netgen 이다.

$ cd ~/ETRI050_DesignKit/2-6_Lab4_FIR_PE

$ make lvs로그 파일을 살펴보면 다음과 같다.

qflow lvs -T etri050 fir_pe

--------------------------------

Qflow project setup

--------------------------------

Technology set to etri050

Regenerating files for existing project fir_pe

Warning: No migration logfile found.

Running netgen

netgen -batch lvs "fir_pe.spice fir_pe" \

"synthesis/fir_pe.spc fir_pe" \

etri050_setup.tcl comp.out -json -blackbox

......

Contents of circuit 1: Circuit: 'fir_pe'

Circuit fir_pe contains 847 device instances.

Class: OR2X2 instances: 8

Class: AOI22X1 instances: 17

Class: NOR2X1 instances: 62

......

Class: DFFPOSX1 instances: 75

Class: INVX8 instances: 1

Circuit contains 865 nets.

Contents of circuit 2: Circuit: 'fir_pe'

Circuit fir_pe contains 847 device instances.

Class: OR2X2 instances: 8

Class: AOI22X1 instances: 17

Class: NOR2X1 instances: 62

......

Class: DFFPOSX1 instances: 75

Class: INVX8 instances: 1

Circuit contains 865 nets.

Circuit 1 contains 847 devices, Circuit 2 contains 847 devices.

Circuit 1 contains 865 nets, Circuit 2 contains 865 nets.

Final result:

Circuits match uniquely.

SPICE 네트리스트 양식으로 표현된 두 회로가 완벽히 일치한다는 결과를 얻었다.

ii-7. DRC: 디자인 룰 검사

레이아웃은 반도체 공정도면의 기하학적 표현이다. DRC(Design Rule check)는 레이아웃(평면도)이 반도체 제조 공장에서 허용하는 정밀도의 한계를 준수하고 있는지 검사한다. DRC를 수행하는 도구는 Magic 이다. 자동배선까지 끝낸 레이아웃 fir_pe.mag 이 저장된 디렉토리로 이동한 후 Magic을 실행한다.

$ cd ~/ETRI050_DesignKit/Tutorials/2-6_Lab4_FIR_PE/layout

$ magic -d XR fir_pe.mag

레이아웃을 편집할 수 있는 그림 창과 tcl 명령창이 열린다. 명령창에 DRC 기능을 켜고 포이터(마우스) 커서의 스냅을 해제한다.

% drc on

% grid off; snap grid

그림 창 의 메뉴 Options>DRC Manager 를 선택하면 디자인 룰을 위배한 목록을 보여주는 창이 열린다.

DRC 항목을 내려보면 위배된 지점의 위치가 나열된다. 해당 지점을 선택하고 확대(Zoom) 버튼을 누르면 오류가 난 지점을 보여준다.

하위 셀의 비아(via)가 배선으로 사용된 금속2(Metal2)와 너무 가깝다. 오류난 지점에 마우스 커서를 놓고 select 명령의 단축키 's' 를 눌러 동일 네트 인지 확인 한다. 동일 네트는 금속2로 메꿔준다.

나머지 오류도 모두 수정해 준다. 디자인 룰 오류가 해소되었는지 최종 확인한다. 표준 셀들이 배치될때 인접한 셀들 사이에 전원과 접지가 공유되도록 겹쳐 있다. 이는 계층적 레이아웃을 평활화(flatten)하면 해결될 것이므로 오류에서 제외한다.

불필요에 하게 표시된 에러 레이어를 삭제한다. 디자인 룰을 적용한 레이아웃을 저장하고 종료한다.

% view

% select top cell

% drc off

% erase errors

% save fir_pe

% quit

수동으로 레이아웃이 편집되었다. 아무리 세심하게 수정 했더라도 실수로부터 자유로울 수 없다 수정한 레이아웃에서 회로 네트리스트를 추출하여 LVS 검사를 실시한다.

Magic 레이아웃 파일에서 SPICE 네트리스트를 추출하는 스크립트를 디자인 킷 scripts 디렉토리에 작성해 두었다.

$ ~/ETRI050_DesignKit/scripts/extract_spice.sh fir_pe

netgen 으로 LVS 를 실시한다.

$ netgen -noc -batch lvs \

"fir_pe.spice fir_pe" "../synthesis/fir_pe.spc fir_pe" \

~/ETRI050_DesignKit/tech/etri050_setup.tcl \

LVS_fir_pe.txt

레이아웃에서 추출한 네트리스트 fir_pe.spice 와 합성으로 생성된 네트리스트 ../synthesis/fir_pe.spc 를 트랜지스터 회로 수준에서 비교한다. LVS 결과 로그는 LVS_fir_pe.txt다.

Subcircuit summary:

Circuit 1: NAND2X1 |Circuit 2: NAND2X1

-----------------------------------|---------------------------------

pfet (2) |pfet (2)

nfet (2) |nfet (2)

Number of devices: 4 |Number of devices: 4

Number of nets: 6 |Number of nets: 6

---------------------------------------------------------------------

Netlists match uniquely.

...........

Circuit 1: INVX8 |Circuit 2: INVX8

-----------------------------------|---------------------------------

Y |Y

A |A

vdd |vdd

gnd |gnd

---------------------------------------------------------------------

Cell pin lists are equivalent.

Device classes INVX8 and INVX8 are equivalent.

Subcircuit summary:

Circuit 1: fir_pe |Circuit 2: fir_pe

-----------------------------------|---------------------------------

NAND2X1 (147) |NAND2X1 (147)

OAI22X1 (7) |OAI22X1 (7)

DFFPOSX1 (75) |DFFPOSX1 (75)

......

CLKBUF1 (8) |CLKBUF1 (8)

INVX2 (10) |INVX2 (10)

INVX8 (1) |INVX8 (1)

Number of devices: 847 |Number of devices: 847

Number of nets: 865 |Number of nets: 865

---------------------------------------------------------------------

Netlists match uniquely.

Subcircuit pins:

Circuit 1: fir_pe |Circuit 2: fir_pe

-----------------------------------|-------------------------

Vld |Vld

Yin[1] |Yin[1]

Yin[2] |Yin[2]

Xout[0] |Xout[0]

Xout[1] |Xout[1]

...... ......

Yout[3] |Yout[3]

Rdy |Rdy

Cin[3] |Cin[3]

Cin[1] |Cin[1]

Cin[5] |Cin[5]

Cin[0] |Cin[0]

clk |clk

gnd |gnd

vdd |vdd

Xin[3] |Xin[3]

......

---------------------------------------------------------------------

Cell pin lists are equivalent.

Device classes fir_pe and fir_pe are equivalent.

Final result: Circuits match uniquely.

netgen 의 LVS 는 SPICE 네트리스트 양식을 가지고 두 회로의 하위 회로 트랜지스터에서부터 배선된 네트, 입출력 포트까지 상당히 정밀하게 비교해준다.

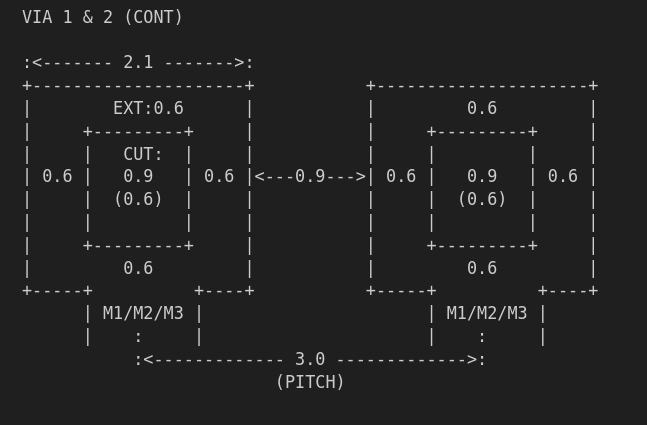

iii. 적층 비아 검사(Stacked Via Check)

비아 (VIA)는 인접 금속층 사이의 접점이다. 비아를 겹쳐 놓아 다층 금속 간 접점을 만들기도 하지만 "내 칩 MPW" 공정은 적층 비아(Stacked VIA)를 허용하지 않는다.

자동 배선 도구 qrouter 가 적층 비아를 활용하지 않도록 Qflow 프로젝트 파일 project_vars.sh 에 다음과 같이 설정해 놓았다.

set via_stacks = none

하지만 qrouter는 완벽히 차단하지 못하기 때문에 이를 찾아내 수정해 주어야 한다. 경희대학교 표준 셀 디자인 킷은 적층 비아를 찾아내는 파이썬 스크립트 check_via_stack.py 를 제공한다. 이 스크립트의 명령줄 사용법은 다음과 같다.

먼저 레이아웃이 저장된 폴더로 이동 후,

$ cd ~/ETRI050_DesignKit/2-6_Lab4_FIR_PE

$ cd layout

적층 비아 검사 스크립트 실행,

$ ~/ETRI050_DesignKit/scripts/check_via_stack.py fir_pe m2contact m3contact 6

Mult=1 / Div=2

Stacked #1

<< m2contact >> rect 5453 2273 5467 2287

<< m3contact >> rect 5453 2273 5467 2287

Box(Scaled): 2726 1136 2733 1143

Stacked #2

<< m2contact >> rect 553 633 567 647

<< m3contact >> rect 553 633 567 647

Box(Scaled): 276 316 283 323

Stacked #3

<< m2contact >> rect 2153 633 2167 647

<< m3contact >> rect 2153 633 2167 647

Box(Scaled): 1076 316 1083 323

Stacked #4

<< m2contact >> rect 1013 113 1027 127

<< m3contact >> rect 1013 113 1027 127

Box(Scaled): 506 56 513 63

***************************************

4 Stacked Contact and/or Via found!

Magic layout "fir_pe_Stacked.mag" created with DRC error layer

Magic 레이아웃 fir_pe.mag을 읽어 VIA1(m2contact, 금속1 과 2층의 접점)과 VIA2(m3contact, 금속2 와 3층의 접점)의 중심 간격이 6 그리드(1.8um) 이내인 경우 겹침으로 판정하여 이를 에러 레이어로 표시하고 fir_pe_Stacked.mag 에 저장한다.

겹친 비아 검사로 발견된 4개의 비아를 수정해준다.

$ magic -d XR fir_pe_Stacked

전체 도면에서 겹친 비아로 표시된 위치를 찾기 위해 명령창에 다음과 같은 명령을 수행한다. 겹친 비아는 실제로 drc 오류는 아니지만 겹친 비아를 검사하면서 레이아웃에 오류 표기를 해놓았다.

% view

%select top cell

% expand

% drc find next

Error area #1:

Error area #2:

Error area #3:

Error area #4:

위의 명령으로 4곳의 오류 영역 중 하나가 편집 상자로 선택된다. 상자를 확대해보자.

% findbox zoom

두 비아가 완전히 겹쳐 있어서 외형적으로 구분되지 않는다. 커서 상자 영역을 선택하여 레이어를 조회하면 두 메탈 컨택이 있다고 알려준다.

% select area

% what

두 비아 중 하나를 골라 이동시켜 겸친 비아를 해소한다.

겹친 비아를 찾아 모두 오류를 수정해 준다. 아래 명령으로 다음 겹친 비아를 찾아 상자를 이동 시킨 후 확대,

% drc find next; findbox zoom

키보드 단축 키를 사용하면 레이아웃 편집이 수월하다. 레이어 편집 시 유용한 Magic의 키보드 단축키는 아래와 같다.

v - view 전체 보기

x - expand 하위 셀 내부 보기 확장

X - un-expand 하위 셀 내부 감추기

z - zoom in 확대

Z - zoom out 축소

s - select 마우스 포인터 아래 레이어 선택

a - select area 상자 아래 레이어 선택

숫자키 패드:

5 - zoom box 상자 영역확대

4/8/6/2 - move left/up/right/down 선택된 레이어 이동

화살표 키:

pan left/up/right/down 화면 이동

겹친 비아를 모두 해소된 레이아웃을 저장하고 Magic 종료,

% view

% select top cell

% erase errors

% save fir_pe

적층 비아 검사를 다시 실시하여 모두 해소 되었는지 확인한다.

$ ~/ETRI050_DesignKit/scripts/check_via_stack.py fir_pe m2contact m3contact 6

편집한 레이아웃에 대하여 네트리스트 추출과 LVS 검사를 반복적으로 실시한다.

$ ~/ETRI050_DesignKit/scripts/extract_spice.sh fir_pe

$ netgen -noc -batch lvs \

"fir_pe.spice fir_pe" "../synthesis/fir_pe.spc fir_pe" \

~/ETRI050_DesignKit/tech/etri050_setup.tcl \

LVS_fir_pe.txt

Magic을 그래픽 편집 창 없이 명령줄 만 띄워 디자인 룰 검사 재실시 한다.

$ magic -dnull -noconsole

Magic의 tcl 명령줄 프롬프트에서 drc 를 수행 하는 절차는 아래와 같다.

% box 0 0 0 0

% load vtop.mag -force

% select top cell

% drc on

% drc check

% drc statistics

% drc count

% drc find next

레이아웃 편집과 LVS 검사 및 DRC 를 반복적으로 수행 하면서 위의 명령들 일일이 입력하기 지루하다. 배쉬 쉘 스크립트를 만들어 두고 활용하면 편리하다.

LVS 검사 쉘 스크립트 run_lvs.sh 는 다음과 같다.

#!/usr/bin/bash

if [[ $# -ne 1 ]]; then

echo " <Layout Name> missing."

exit 2

fi

# Extract Spice for LVS

~/ETRI050_DesignKit/scripts/extract_spice.sh $1

# LVS check with Synthesis netlist

netgen -noc -batch lvs \

"$1.spice $1" \

"../synthesis/$1.spc $1" \

~/ETRI050_DesignKit/tech/etri050_setup.tcl \

LVS_$1.txt

DRC 쉘 스크립트 run_drc.sh 는 다음과 같다.

#!/usr/bin/bash

if [[ $# -ne 1 ]]; then

echo " <Layout Name> missing."

exit 2

fi

drc off

box 0 0 0 0

load $1.mag -force

view

select top cell

select area

expand

drc on

drc check

drc count

drc why

drc statistics

box

quit -noprompt

EOF

쉘 스크립트를 활용, LVS 검사를 실시하여 합성 네트리스트와 레이아웃 네트리스트가 등가임을 확인한다.

$ ~/ETRI050_DesignKit/scripts/run_lvs.sh fir_pe

Circuit 1 contains 847 devices, Circuit 2 contains 847 devices.

Circuit 1 contains 865 nets, Circuit 2 contains 865 nets.

Final result:

Circuits match uniquely.

쉘 스크립트를 활용, DRC 를 실시하여 디자인 룰 오류가 없음을 확인한다.

$ ~/ETRI050_DesignKit/scripts/run_drc.sh fir_pe

Total DRC errors found: 0

This layer can't abut or partially overlap between subcells

Design-rule checker statistics (recent/total):

Squares processed: 0/0

Tiles processed: 250731/250731

Edges pieces processed: 514947/514947

Constraint areas checked: 2535603/2535603

Multi-tile constraints: 1833408/1833408

Interaction areas processed: 72/72

Tiles processed for interactions: 250731/250731

Tiles processed for arrays: 0/0

Root cell box:

width x height ( llx, lly ), ( urx, ury ) area (units^2)

microns: 895.050 x 832.050 (-9.450, -3.600), ( 885.600, 828.450) 744726.375

lambda: 2983.50 x 2773.50 (-31.50, -12.00), ( 2952.00, 2761.50) 8274737.00

internal: 5967 x 5547 ( -63, -24 ), ( 5904, 5523 ) 33098949

iv. 레이아웃 네트리스트 시뮬레이션

소규모 소자가 포함된 셀(기초 디지털 또는 아날로그 라이브러리)의 경우 전기적 특성을 세밀히 관찰할 목적으로 레이아웃에서 추출한 SPICE 양식의 트랜지스터 네트리스트를 가지고 회로 시뮬레이션 할 수 있다.

"내 칩 MPW" 만 해도 수천개의 트랜지스터를 가진 회로다. 회로 시뮬레이션은 수행 시간을 따져봐도 불가능하다. 이를 극복할 목적으로 다양한 방법론이 제안되었지만 뾰족한 방안은 없다. 회로 시뮬레이션 대신 기능 모델(Bus Functional Model) 수준에서 수행되지만 이 역시 하드웨어와 소프트웨어 융합된 시스템 수준에는 한없이 느리다. 이를 극복할 방법으로 시뮬레이션 가속기, 에뮬레이션 등의 방법이 있으나 비용과 수고에 비하면 큰 효과를 보여주지 못한다. FPGA를 사용한 고속 프로토타이핑(fast proto-typing)이 가장 현실적이다.

중소규모의 디지털 회로에 한하여 스위칭 수준 시뮬레이션을 수행할 수 있다. 레이아웃 에서 추출한 SPICE 네트리스트의 트랜지스터를 스위치로 간주하고 논리 검증을 실시한다. 오픈-소스 스위치 수준 시뮬레이터는 irsim이다.

디자인 킷 튜토리얼에 Magic 의 레이아웃에서 트랜지스터 네트리스트 추출하는 스크립트가 준비되어 있다.

$ cd ~/ETRI050_DesignKit/Tutorials/2-6_Lab4_FIR_PE

$ cd irsim

$ ~/ETR1050_DesignKit/scripts/ext2sim.sh ../chip_top/fir_pe_Core

irsim용 네트리스트 파일은 fir_pe_Core.sim이다. 기초적인 전기특성 파일과 함께 스위치 수준 시뮬레이터를 실행 한다.

$ irsim ~/ETRI050_DesignKit/digital_ETRI/khu_etri050.prm fir_pe_Core.sim

irsim의 명령줄에서 테스트 명령 스크립트를 읽는다.

% source fir_pe_Core.tcl

irsim의 사용자 인터페이스는 tcl의 대화형 명령 처리기(interpreter)에 irsim용 명령어를 추가하여 개발되었다. 따라서 tcl의 스크립트 문법체계에 의한 프로시져(함수)를 기술 할 수 있다. 전통적으로 많은 전자 설계 자동화 EDA 도구들의 사용자 인터페이스로 tcl을 채택하고 있으므로 익혀두면 유용하다. 테스트벤치 tcl 스크립트 fir_pe_Core.tcl에 반복적인 테스트 입력을 주고 시뮬레이션을 진행하는 반복적인 명령을 주기 위한 프로시져 sim{} 가 포함되어 있다.

간단한 시험을 위해 아래와 같이 입력을 주어본다.

% sim 1 1 1

% sim 1 1 1

% sim 1 1 1

% sim 1 1 1

Xin, Cin, Yin 을 모두 1로 주고 3번 반복하면,

1*1+1 = 2

좀더 복잡한 값을 넣어보자.

% sim 4 20 100

% sim 4 20 100

% sim 4 20 100

% sim 4 20 100

결과는,

4*20+100 = 180($00b4)

레이아웃에서 추출한 트랜지스터 회로의 스위칭 모델 시뮬레이션이다.

v. 입출력 패드 부착(IO Pad)

이제 마이크로미터의 세계에서 미리미터의 세계로 옮겨갈 단계에 왔다. 반도체 부품은 결국 인간의 인지영역에서 사용된다. 적어도 기판에 땜을 하려면 미리미터 단위로 옮겨와야 한다. 마이크로 단위의 세계는 크기 만큼이나 작동에 필요한 에너지량도 매우 적다. CMOS 트랜지스터의 작동에 필요한 에너지는 나노 와트에 불과하다. 자연계에 부유하는 에너지에 과도하게 반응하거나 견디지 못히고 파괴되기도 한다. 마이크로 세계의 트랜지스터를 보호하고 의미있는 신호만을 걸러내는 장치가 입출력 패드(IO Pad)다.

"내 칩 MPW" 디자인 킷에 제공된 입출력 패드 셀을 활용 하여 칩을 완성한다. 패키지 칩을 제공 받을 경우 표준칩 배치 레이아웃을 사용하여 최종 GDS 를 생성 한다. 범용 입출력 GPIO 패드들의 목록은 아래와 같다. 전원용 패드 PVDD와 PVSS, 디지털 입력 패드 PIC 그리고 출력용 으로 3종류의 패드 셀이 제공된다.

Digital Output: POB24/POB8/POB4

Digital Input: PIC

VDD: PVDD

VSS: PVSS

v-1. 최상위 레이아웃 작업 디렉토리, chip_top

검증이 완료된 설계에 입출력 패드를 다는 작업을 실시할 디렉토리를 만들고 이동한다.

$ cd ~/ETRI050_DesignKit/Tutorials/2-6_Lab4_FIR_PE

$ mkdir chip_top

$ cd chip_top

레이아웃 디렉토리에서 Magic 의 자원 설정 파일을 복사한다.

$ cp ../layout/.magicrc .

자원설정 파일에 패드 라이브러리의 경로 추가,

addpath ~/ETRI050_DesignKit/pads_ETRI050

LVS와 DRC 검증이 완료된 레이아웃 fir_pe.mag 를 fir_pe_Core.mag 로 복사해온다. 파일 명에 유의한다.

$ cp ../layout/fir_pe.mag fir_pe_Core.mag

"내 칩 MPW"의 28핀 표준 패드 배치 레이아웃 파일 MPW_PAD_28Pin_IO.mag 을 현재 작업 디렉토리에 fir_pe_Top.mag 로 복사해 온다. 복사해온 파일이 읽기 전용이다. 쓰기 가능하도록 속성 변경해준다.

$ cp ~/ETRI050_DesignKit/pads_ETRI050/MPW_PAD_28Pin_IO.mag ./fir_pe_Top.mag

$ chmod +w fir_pe_Top.mag

v-2. 칩 마킹/로고(Chip Marking/Logo)

칩 귀퉁이에 내 칩의 고유 표시를 남기고 싶다면 금속 층으로 MY_LOGO.mag 를 그려두어도 좋다. 또는 디자인 킷에 2비트 흑백 이미지를 .mag 로 변환해주는 파이썬 스크립트가 있다.

아래와 같은 MY_LOGO.bmp 이미지를,

변환하면,

$ ~/ETRI050_DesignKit/scripts/bmp2mag_m123.py MY_LOGO.bmp

다음과 같은 레이아웃을 얻을 수 있다.

설계 코어에 입출력 패드를 달 준비되었다. 최상위 레이아웃 작업 디렉토리, chip_top에 있어야 할 파일들은 다음과 같다.

$ ~/ETRI050_DesignKit/Tutorials/2-6_Lab4_FIR_PE/chip_top$ ll

total 2364

drwxr-xr-x 2 goodkook goodkook 4096 Aug 25 07:42 ./

drwxr-xr-x 8 goodkook goodkook 4096 Aug 20 21:13 ../

-rw-r--r-- 1 goodkook goodkook 663862 Aug 20 21:42 fir_pe_Core.mag

-rw-r--r-- 1 goodkook goodkook 7129 Aug 25 07:42 fir_pe_Top.mag

-rw-r--r-- 1 goodkook goodkook 487 Aug 20 21:15 .magicrc

-rw-r--r-- 1 goodkook goodkook 12062 Aug 20 21:30 MY_LOGO.mag

v-3. 패드 배치 계획(Chip-Top plan)

최상위 칩 fir_pe_Top 에 검증이 완료된 코어 셀 fir_pe_Core을 배치하고 입출력 패드 계획을 세운다.

$ magic -d XR fir_pe_Top

% getcell fir_pe_Core

% getcell MY_LOGO

코어 셀을 확장한 후,

% view

% select cell fir_pe_Core_0

% expand

포트를 위치 확인한다.

% goto fir_pe_Core_0/clk

% findbox zoom

Magic의 명령줄은 tcl 문법을 따르기 때문에 대괄호를 직접 쓸 수 없다. 중괄호로 묶는다.

% goto {fir_pe_Core_0/Xin[0]}

코어의 모든 포트를 찾아 인접한 패드와 배선 계획을 세운다.

범용 코어 fir_pe_Core의 포트와 패드 위치 그리고 사용할 패드 라이브러리를 골라 다음과 같이 입출력 패드 계획을 세웠다. 코어의 포트 이름은 베릴로그 문법에서 유래하여 대괄호가 사용되고 있지만 일부 자동화 도구와 호환성이 없으므로 인스턴스 이름을 붙일 때 밑줄로 변경해 주는 것이 좋다. 이름에 대소문자 구분하지 않는다. 입력 포트의 패드 셀은 PIC를, 출력 포트의 패드 셀은 POB8을 선택 했다. 따라붙은 숫자는 구동력(driving power)을 나타낸다. POB8은 구동력 8mA 다.

IO-Pad plan: fir_pe_Top

-----------------------

Port PAD# IO-PAD Instance

Name Cell Name Name

------- ------ -------- --------

Xout[0] PAD_0 POB8 XOUT_0

Xin[1] PAD_1 PIC XIN_1

Xout[1] PAD_2 POB8 XOUT_1

Cin[0] PAD_3 PIC CIN_0

Cin[1] PAD_4 PIC CIN_1

Xin[0] PAD_5 PIC XIN_0

Cin[2] PAD_6 PIC CIN_2

Cin[4] PAD_7 PIC CIN_4

Cin[5] PAD_8 PIC CIN_5

Xout[3] PAD_9 POB8 XOUT_3

Xout[2] PAD_10 POB8 XOUT_2

GND PAD_11 PVSS VSS_0

Cin[3] PAD_12 PIC CIN_3

Xin[3] PAD_13 PIC XIN_3

Xin[2] PAD_14 PIC XIN_2

Yin[0] PAD_15 PIC YIN_0

Yin[1] PAD_16 PIC YIN_1

Yin[2] PAD_17 PIC YIN_2

Yin[3] PAD_18 PIC YIN_3

Yout[1] PAD_19 POB8 YOUT_1

Yout[3] PAD_20 POB8 YOUT_3

Yout[2] PAD_21 POB8 YOUT_2

Yout[0] PAD_22 POB8 YOUT_0

clk PAD_23 PIC CLK

Vld PAD_24 PIC VLD

VDD PAD_25 PVDD VDD_0

Rdy PAD_26 PIC RDY

코어와 로고가 배치된 최상위 레이아웃 fir_pe_Top 을 저장한 후 Magic 종료,

% save fir_pe_Top

% quit

v-4. 패드 배치 및 배선(Edit Chip-Top & Pad routing)

입출력 패드의 배치와 코어 사이의 배선은 수동으로 이뤄진다. 매우 세심한 주의가 요구된다.

패드 배치를 Magic의 레이아웃 그래픽 편집 창에서 입출력 패드를 찾아 변경할 수 있지만 매우 번거롭다. 문서 편집기로 fir_pe_Top.mag 를 열어 위의 계획 편집하는 편이 수월하다.

패드 배선을 위해 최상위 레이아웃을 읽는다.

$ magic -d XR fir_pe_Top

Magic 에서 외부의 GDS 형식을 들여와 활용 할 수 있다. GDS는 마스크 제작용 레이아웃 형식이다. 레이어 번호, 비아와 컨택 컷 생성 등 Magic 의 편집 체계에 맞지 않으므로 들여오려면 변환 규칙이 필요하다. 이 규칙은 경희대학교 디자인 킷의 Magic 테크파일에 기술되어 있다. 외부 GDS 들여오기 규칙명(tech. name)은 ETRI-G 다. "내 칩 MPW" 디자인 킷에서 제공한 GDS 형식의 GPIO 패드 라이브러리를 Magic 으로 읽어들이는 절차는 다음과 같다.

cif istyle lambda=0.30(ETRI-G)

cif ostyle lambda=0.30(ETRI-G)

gds read ~/ETRI050_DesignKit/pads_ETRI050/ETRI_NSPL_GPIO_231208_Klayout.gds

미리 작성해둔 GPIO GDS 읽기 스크립트는 load_gpio_gds.tcl 다. Magic 명령창에서 스크립트를 수행한다.

% source ~/ ETRI050_DesignKit/pads_ETRI050/load_gpio_gds.tcl

최상위 레이아웃을 다시 읽으면 코어를 비롯하여 GPIO 패드까지 내부를 볼 수 있다.

% load fir_pe_Top

% select top cell

% expand

패드 계획대로 수정한 최상위 레이아웃 fir_pe_Top 을 읽어 코어와 패드 배선을 수행한다. 패드 배선은 금속 2와 3층을 사용한다. 배선이 매우 길어진다. 배선 굵기는 3~4um 로 하자. 위 그림은 패드 배선까지 마친 최상위 레이아웃이다. 배선까지 마쳤으면 저장 후 종료한다.

vi. 최종 GDS 생성(Final GDS generation)

패드 배선까지 마친 최상위 레이아웃에는 3가지 상이한 조건의 하위 레이아웃을 포함한다.

1. 코어(Core): DRC와 LVS 검증된 레이아웃이다. 비아와 컨택 컷이 생성되기 전이다.

2. 입출력 패드(GPIO Pad): 외부에서 GDS로 공급된 라이브러리다. 비아와 컨택 컷이 이미 공정률에 맞춰 생성되었기 때문에 Magic 의 디자인 룰 검사를 수행할 수 없다.

3. 코어-패드 배선(Core-Pad Routing): 코어와 패드 사이의 배선을 수동으로 실시하였다. DRC 검사가 필요하다.

최상위 레이아웃에서 위의 3부분을 각각 분리한 후 개별적인 검사와 GDS를 생성다. 파이썬 스크립트 xPad.py 로 패드 부분만 분리한다.

$ ~/ETRI050_DesignKit/scripts/xPad.py fir_pe

코어와 패드 배선 부분만 분리해 내는 스크립트는 xPin_Route.py다.

$ ~/ETRI050_DesignKit/scripts/xPin_Route.py fir_pe

분리 작업을 수행한 후 디렉토리 내 파일목록을 확인한다.

~/ETRI050_DesignKit/Tutorials/2-6_Lab4_FIR_PE/chip_top$ ll

total 2408

drwxr-xr-x 2 goodkook goodkook 4096 Aug 25 18:47 ./

drwxr-xr-x 8 goodkook goodkook 4096 Aug 20 21:13 ../

-rw-r--r-- 1 goodkook goodkook 696732 Aug 25 11:38 fir_pe_Core.mag

-rw-r--r-- 1 goodkook goodkook 6602 Aug 25 18:45 fir_pe_Pad.mag

-rw-r--r-- 1 goodkook goodkook 3210 Aug 25 18:47 fir_pe_Pin_Route.mag

-rw-r--r-- 1 goodkook goodkook 9753 Aug 25 15:38 fir_pe_Top.mag

-rw-r--r-- 1 goodkook goodkook 487 Aug 20 21:15 .magicrc

-rw-r--r-- 1 goodkook goodkook 12062 Aug 20 21:30 MY_LOGO.bmp

-rw-r--r-- 1 goodkook goodkook 1622945 Aug 25 07:53 MY_LOGO.bmp.mag

-rw-r--r-- 1 goodkook goodkook 88833 Aug 20 21:35 MY_LOGO.mag

최상위 레이아웃에서 코어의 좌표를 구한다.

$ magic -d XR fir_pe_Top.mag

% select fir_pe_Core_0

% box

GDS 병합에 필요한 코어의 좌측 하단(lower-left) 좌표는 (484.250um, 541.850um) 다. 이어서 코어와 패드 사이의 배선을 열어 DRC를 수행하고 좌표를 구한다.

$ magic -d XR fir_pe_Pin_Route.mag

% select top cell

% drc on

% drc check

% drc why

% box

배선에 DRC 오류는 없다. box 명령으로 fir_pe_Pin_Route 의 좌측하단 좌표가 (441.0um, 441.0um) 를 확인 한다. 다음은 패드 프레임의 좌표 구하기다. 외부에서 GDS로 공급된 라이브러리이므로 DRC 절차는 필요없다.

$ magic -d XR fir_pe_Pad.mag

% select top cell

% box

패드 프레임의 좌측하단 좌표는 (97.5um, 97.5um) 임을 확인 한다.

분리했던 각 부분 레이아웃에 대하여 GDS를 생성하고 병합한 후 최종적으로 평탄화된 GDS를 생성한다. 이 작업은 다소 복잡한데 경희대학교 디자인 킷에 제공하는 스크립트를 사용한다.

$ ~/ETRI050_DesignKit/scripts/generate_chip.sh

usage: generate_chip <core name> <pad_x> <pad_y> <route_x> <route_y> <core_x> <core_y>

코어 이름과 앞서 구한 좌표들을 주고 스크립트 실행,

$ ~/ETRI050_DesignKit/scripts/generate_chip.sh fir_pe 97.5 97.5 441.0 441.0 484.250 541.850

........

fir_pe_Core_F: 410000 rects

fir_pe_Core_F: 420000 rects

CIF output style is now "lambda=0.30(ETRI-G)"

Generating output for cell fir_pe_Top_F

성공적으로 무려 40만개 이상의 사각형 스티치가 포함된 최종 GDS가 생성되었다. GDS 파일 크기는 34Mbyte 에 달한다.

$ ll *.gds

-rw-r--r-- 1 goodkook goodkook 34220354 Aug 25 19:32 fir_pe_Top.gds

vii. GDS 복기 (Review GDS)

klayout 으로 생성된 최종 GDS를 복기해본다.

$ klayout

GDS는 공정 마스크 제작용 파일이다. 레이어들이 숫자로 표시된다. 이름을 표시하려면 File 메뉴에서 레이어 속성을 읽는다.

File > Load Layer Properties > ~/ETRI050_DesignKit/devel/scripts/ETRI050_CMOS.lyp

수많은 사각형을 육안으로 검사하기는 곤란하지만 들여다 보면 다소나마 안심이 된다. 먼저 겹친 비아가 있는지 확인해 보자. 표시 레이어를 VIA1과 2로 한정했다.

입력 패드에 과전류 제한 고저항 Poly2와 정전기 방지 ESD 레이어가 있다.

그외 각 레이어들을 살펴보며 확인해 보자.